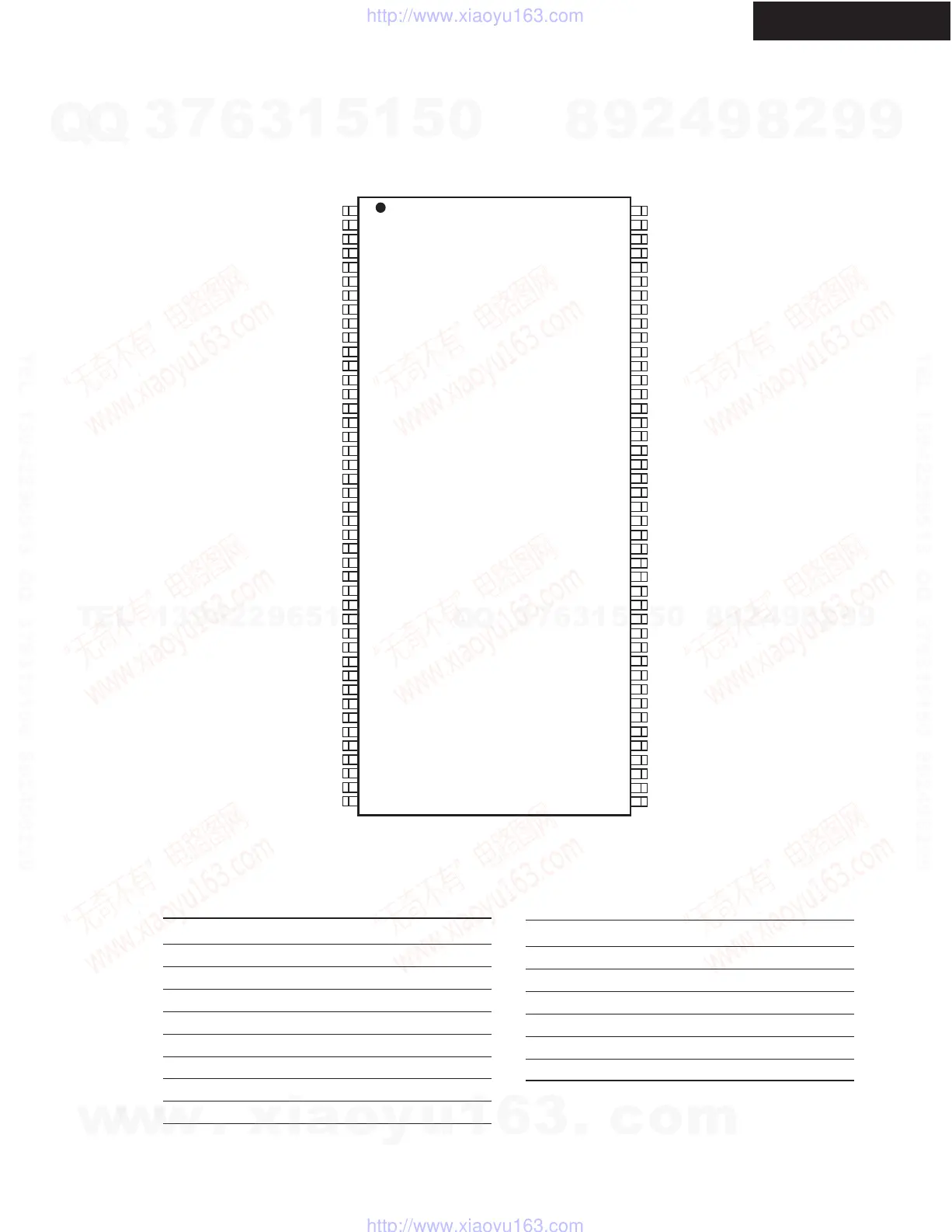

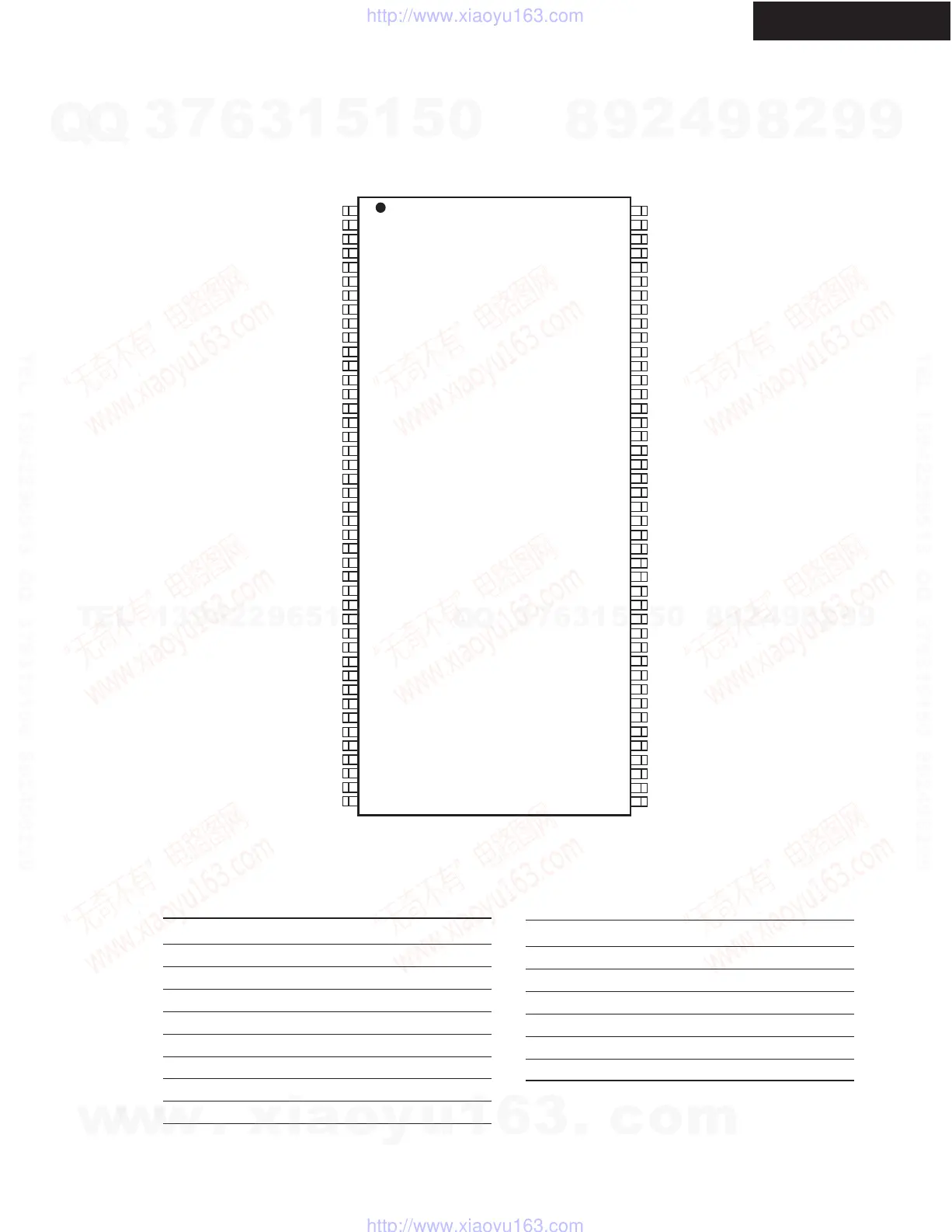

PIN CONFIGURATION

IC BLOCK DIAGRAMS AND TERMINAL DESCRIPTIONS -27

Q3461, Q3561 : IS42S32200E-6TL (64 Mbit SD RAM)

TX-SR806/SA806

PIN DESCRIPTIONS

A0-A10 Row Address Input

A0-A7 Column Address Input

BA0, BA1 Bank Select Address

DQ0 to DQ31 Data I/O

CLK System Clock Input

CKE Clock Enable

CS

Chip Select

RAS

Row Address Strobe Command

CAS

Column Address Strobe Command

V

DD

DQ0

V

DD

Q

DQ1

DQ2

V

SS

Q

DQ3

DQ4

V

DD

Q

DQ5

DQ6

V

SS

Q

DQ7

NC

V

DD

DQM0

WE

CAS

RAS

CS

NC

BA0

BA1

A10

A0

A1

A2

DQM2

V

DD

NC

DQ16

V

SS

Q

DQ17

DQ18

V

DD

Q

DQ19

DQ20

V

SS

Q

DQ21

DQ22

V

DD

Q

DQ23

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

V

SS

DQ15

V

SS

Q

DQ14

DQ13

V

DD

Q

DQ12

DQ11

V

SS

Q

DQ10

DQ9

V

DD

Q

DQ8

NC

V

SS

DQM1

NC

NC

CLK

CKE

A9

A8

A7

A6

A5

A4

A3

DQM3

V

SS

NC

DQ31

V

DD

Q

DQ30

DQ29

V

SS

Q

DQ28

DQ27

V

DD

Q

DQ26

DQ25

V

SS

Q

DQ24

V

SS

WE Write Enable

DQM0-DQM3 x32 Input/Output Mask

VDD Power

Vss Ground

VDDQ Power Supply for I/O Pin

Vss Q Ground for I/O Pin

NC No Connection

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...