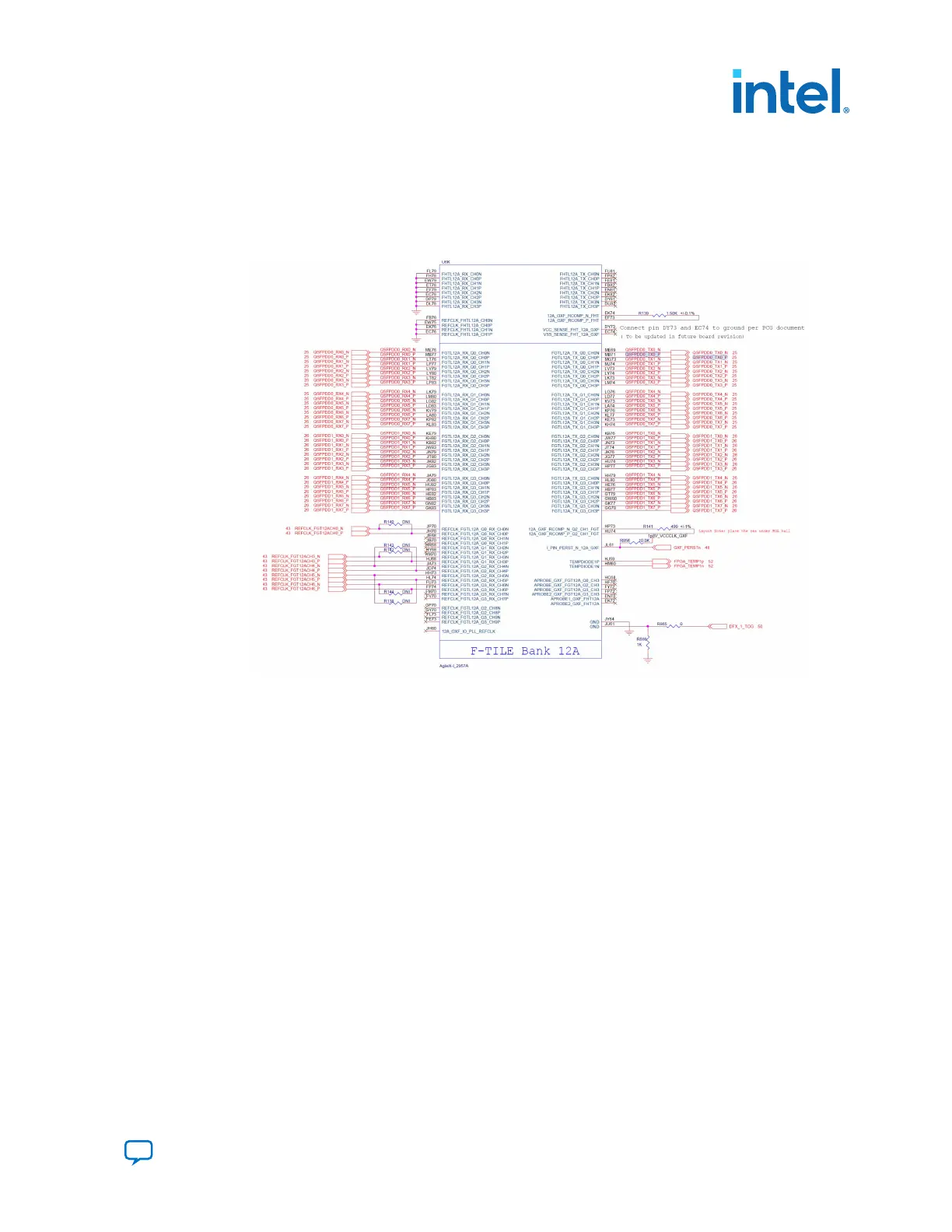

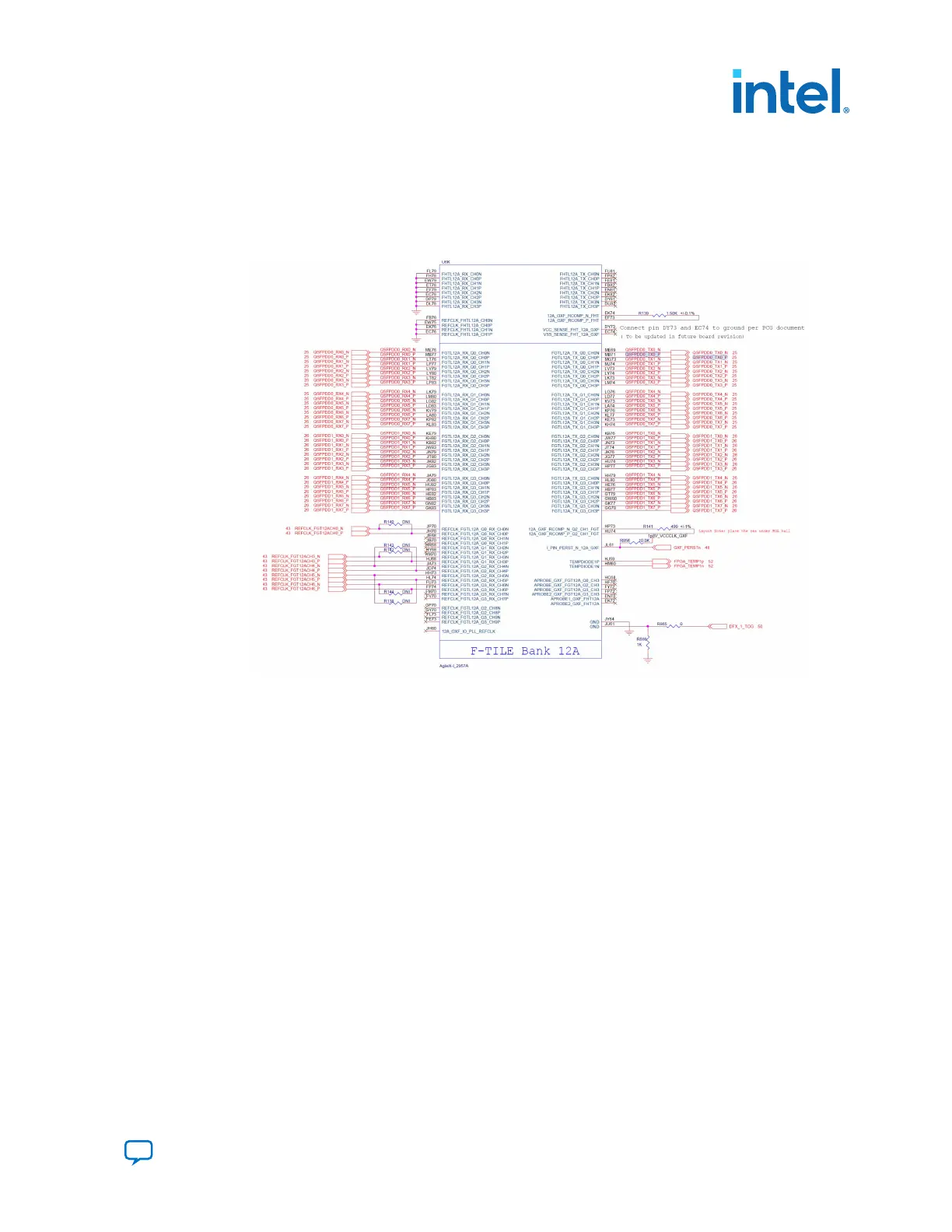

The F-tile (12A) of the FPGA provides 16 general-purpose (FGT) transceiver channels,

each 8-channel group is routed to one QSFPDD. The transceiver bank requires 156.25

MHz clocks for the 28 Gbps NRZ and 325.50 MHz clocks for the 56 Gbps PAM4. These

clocks must have RPM jitter <250fs.

Figure 32. F-Tile Bank 12A Circuit

A.7. Port Controller

A Texas Instrument FPC202 dual-port controller serves as the low-speed signal

aggregator for the two QSFP ports.

A. Development Kits Components

683288 | 2022.09.22

Send Feedback

Intel

®

Agilex

™

I-Series FPGA Development Kit User Guide

45

Loading...

Loading...