Lake Shore Model 325 Temperature Controller User’s Manual

Remote Operation 6-5

6.1.4.1.4 Status Byte Register

The Status Byte register, typically referred to as the Status Byte, is a non-latching, read-only register that contains all of

the summary bits from the register sets. The status of the summary bits are controlled from the register sets as explained

above. The Status Byte also contains the Request for Service (RQS)/Master Summary Status (MSS) bit. This bit is used

to control the Service Request hardware line on the bus and to report if any of the summary bits are set via the *STB?

command. The status of the RQS/MSS bit is controlled by the summary bits and the Service Request Enable Register.

6.1.4.1.5 Service Request Enable Register

The Service Request Enable Register determines which summary bits in the Status Byte will set the RQS/MSS bit of the

Status Byte. The user may write to or read from the Service Request Enable Register. Each Status Byte summary bit is

logically ANDed to the corresponding enable bit of the Service Request Enable Register. When a Service Request

Enable Register bit is set by the user, and the corresponding summary bit is set in the Status Byte, the RQS/MSS bit of

the Status Byte will be set, which in turn sets the Service Request hardware line on the bus.

6.1.4.1.6 Reading Registers

Any register in the status system may be read using the appropriate query command. Some registers clear when read,

others do not. Refer to Section 6.1.4.1.8. The response to a query will be a decimal value that corresponds to the binary-

weighted sum of all bits in the register (Table 6-1). The actual query commands are described later in this section.

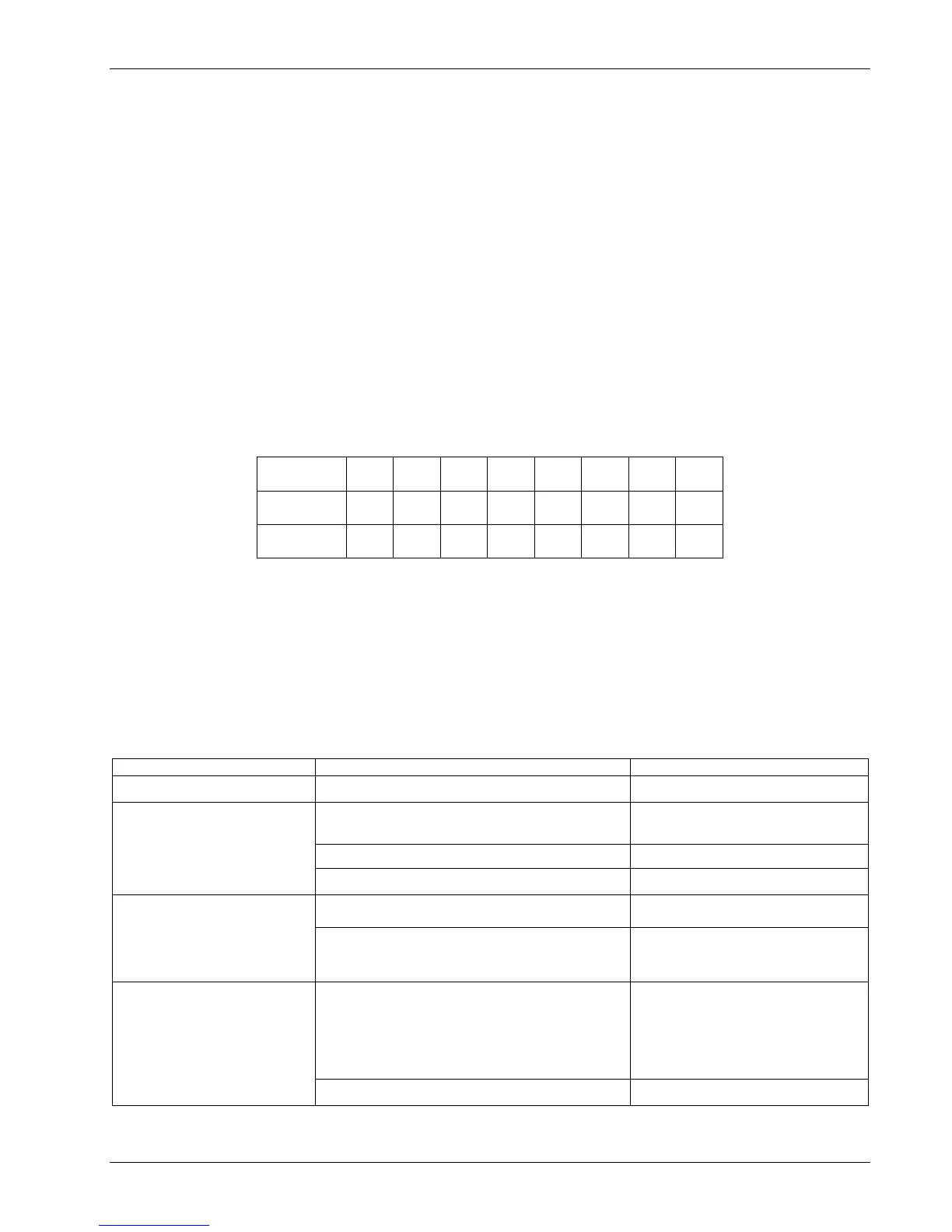

Table 6-1. Binary Weighting of an 8-Bit Register

Example: If bits 0, 2, and 4 are set, a query of the register will return a decimal value of 21 (1+4+16).

6.1.4.1.7 Programming Registers

The only registers that may be programmed by the user are the enable registers. All other registers in the status system

are read-only registers. To program an enable register send a decimal value that corresponds to the desired binary-

weighted sum of all bits in the register, refer to Table 6-1. The actual commands are described later in this section.

6.1.4.1.8 Clearing Registers

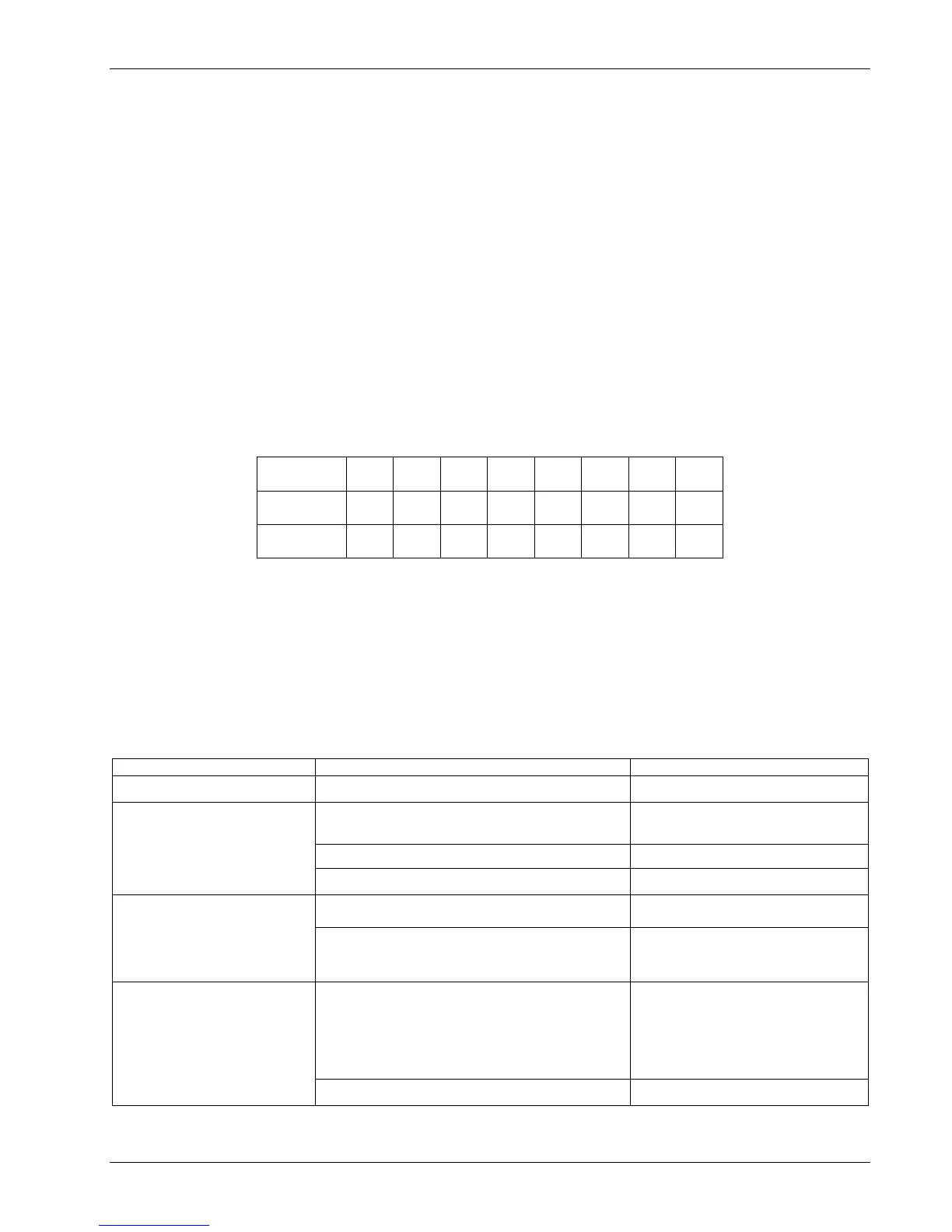

The methods to clear each register are detailed in Table 6-2.

Table 6-2. Register Clear Methods

None — registers are not latched

Standard Event Status Register

Operation Event Register

*ESR? (clears Standard Event Status

register)

*CLS (clears both registers)

Standard Event Status Enable

Register

Operation Event Enable Register

Service Request Enable Register

Write 0 to the enable register

*ESE 0 (clears Standard Event Status

Enable register)

There are no commands that directly clear the Status

Byte as the bits are non-latching; to clear individual

summary bits, clear the event register that

corresponds to the summary bit — sending *CLS

will clear all event registers which in turn clears the

status byte

If bit 5 (ESB) of the Status Byte is set,

send *ESR? to read the Standard Event

Status Register and bit 5 will clear

Loading...

Loading...