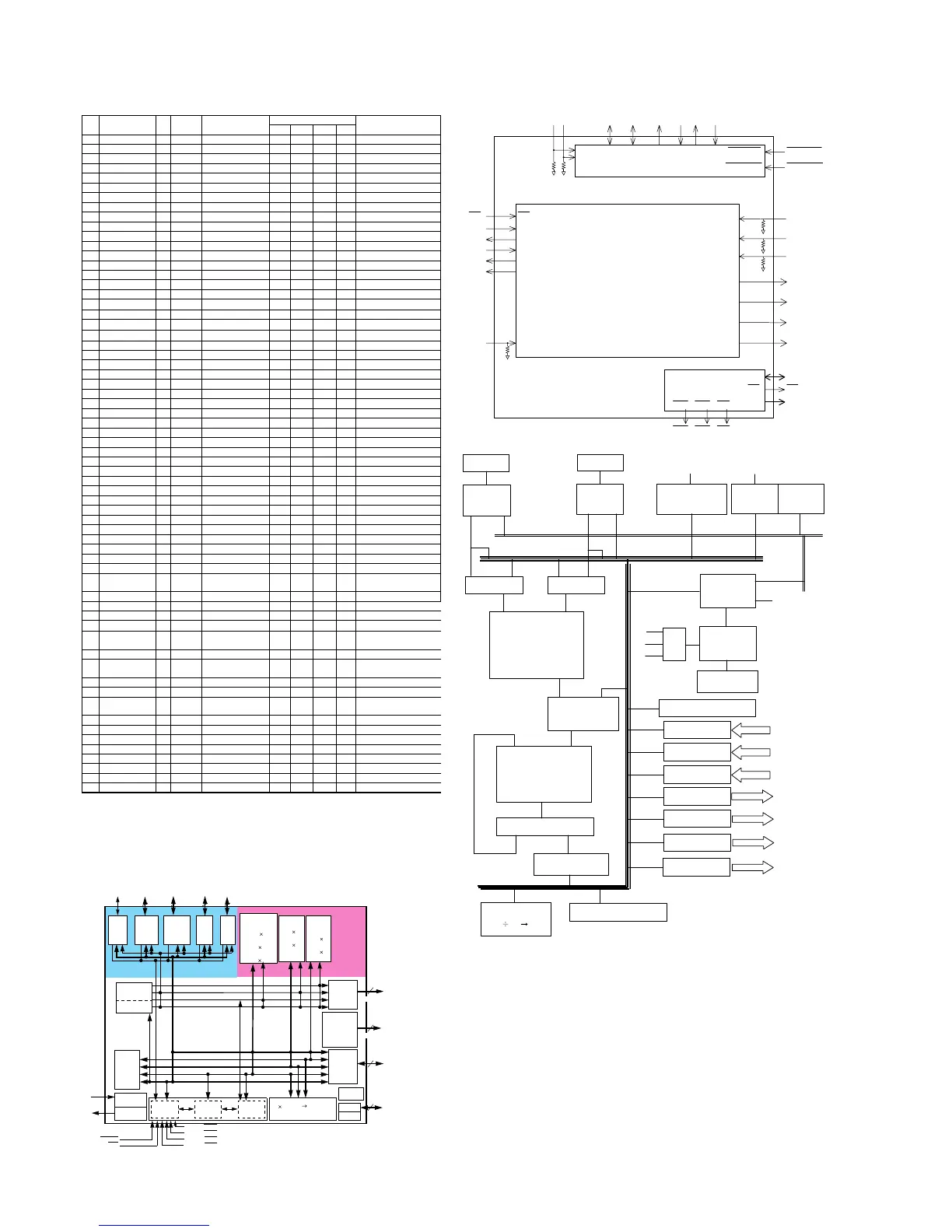

SI

RQ

SO

RDY

DSP RESET

INIT RESET

JX

DRDY DRDY

SI

RQ

SO

SCLK SCLK

RDY

CLKOUTBITCLKLRCLK

SMODE

CTRL

DSP RESET

INIT RESET

TESTI1

TESTI1

SDOUT4

IO7~IO0

OE

A16~A0

WE

RAS CAS

EXTERNAL RAM

IO7~IO0

OE

A16~A0

WE RAS CAS

CONTROLLER

SDOUT3

SDOUT2

SDOUT1

SDOUT4

SDIN1

SDIN2

SDIN3

CP0,CP1

CRAM

384 X 16

DP0,DP1

DRAM

256 X 24

MPX16 MPX24

Data IO7~IO0

Delay Data

16bit

OFRAM

48 X 20

X Y

Multiply

16 X 24 -> 40

Micon I/F

Control

PRAM

512 X 32

DEC

PC

Stack : 1level

MUL DBUS

SHIFT

A B

ALU

34bit

Overflow Margin: 4bit

DR0

~

3

Over Flow Data

Generator

Divider

24 24 16

Peak Detector

TMP 8 X 24bit

2 X 24/20/16 bit

2 X 24/20/16bit

2 X 24/20/16bit

2 X 24bit

2 X 24bit

2 X 24bit

Serial I/F

CBUS(16bit)

DBUS(24bit)

40bit

24bit

34bit

34bit

24bit

SDIN1

SDIN2

SDIN3

SDOUT1

SDOUT2

SDOUT3

Ext RAM

Control

Address A16~A0

2 X 24bit

SDOUT4

Q604 : AK7706VT

Q651(

µ

PD78F0034GC)

Port Setting

Pin Port Name I/O Use Name

Opt. Act. P-Off Stop

Note

1 P50/A8 I/O O A8 Address Bus

2 P51/A9 I/O O A9 Address Bus

3 P52/A10 I/O O A10 Address Bus

4 P53/A11 I/O O A11 Address Bus

5 P54/A12 I/O O A12 Address Bus

6 P55/A13 I/O O A13 Address Bus

7 P56/A14 I/O O A14 Address Bus

8 P57/A15 I/O O A15 Address Bus

9 Vss0 - Vss0 GND GND

10 Vdd0 - Vdd0 +5VD Power Supply

11 P30 I/O O A16 Address Bus

12 P31 I/O O A17 Address Bus

13 P32 I/O O A18 Address Bus

14 P33 I/O I RESERVE Pulled Down

15 P34/SI31 I/O I SI31_HPDSP Serial Input

16 P35/SO31 I/O O SO31_ HPDSP Serial Output

17 P36/SCK31 I/O O SCK31_ HPDSP Serial Clock

18 P20/SI30 I/O O SS_ HPDSP

HPDSP Select

19 P21/SO30 I/O I IF_SW H= Switch, L=SUB2

20 P22/SCK30 I/O O HPDSP _RST L

HPDSP Reset

21 P23/RxD0 I/O O PINIT

HPDSP PINIT

22 P24/TxD0 I/O I RESERVE Pulled Down

23 P25/ASCK0 I/O O HPBUSY H SUB2 Busy Status

24 Vdd1 - Vdd1 +5VD Power Supply

25 Avss - AVss Vss0

26 P17/ANI7 I I RESERVE Pulled Down

27 P16/ANI6 I I RESERVE Pulled Down

28 P15/ANI5 I I HPMUTE H HPDSP Mute

29 P14/ANI4 I I HPFS1 HPDSP FS

30 P13/ANI3 I I HPFS0 HPDSP FS

31 P12/ANI2 I I _HPPD SUB2 System Down

32 P11/ANI1 I I HPMODE1 DH

33 P10/ANI0 I I HPMODE0 DH

34 Avref - Vss0

35 Avdd - Vdd0

36 RESET I I _RESETHP L SUB2 Reset

37 XT2 - - - Vdd0

38 XT1 I I -

39 IC - VPP

40 X2 - X2 8MHz

41 X1 I X1 8MHz

42 Vss1 - Vss1 GND GND

43 P00/INTP0 I I HREQ_ HPDSP HPDSP Request

44 P01/INTP1 I I RESERVE Pulled Down

45 P02/INTP2 I I RESERVE Pulled Down

46 P03/INTP3/

ADTRG

I I RESERVE Pulled Down

47 P70/TI00/TO0 I/O O LED_BYPASS H BYPASS LED

48 P71/TI01 I/O O

LED_DH1

H DH1 LED

49 P72/TI50/TO50 I/O O LED_DH2 H DH2 LED

50 P73/TI51/TO51 I/O O

LED_DH3

H

DH3 LED

51 P74/PCL I/O I _IRQA L_

Edge

MODE A

52 P75/BUZ I/O I RESERVE Pulled Down

53 P64/RD I/O O READ H_

Edge

Read Strobe

54 P65/WR I/O O WRITE

55 P66/WAIT I/O O WAIT Wait

56 P67/ASTB I/O O LATCH L_

Edge

LATCH

57 P40/AD0 I/O I/O AD0 Address/Data Bus

58 P41/AD1 I/O I/O AD1 Address/Data Bus

59 P42/AD2 I/O I/O AD2 Address/Data Bus

60 P43/AD3 I/O I/O AD3 Address/Data Bus

61 P44/AD4 I/O I/O AD4 Address/Data Bus

62 P45/AD5 I/O I/O AD5 Address/Data Bus

63 P46/AD6 I/O I/O AD6 Address/Data Bus

64 P47/AD7 I/O I/O AD7 Address/Data Bus

Loading...

Loading...