2 - 26 2 - 26

MELSEC-Q/QnA

2 INSTRUCTION TABLES

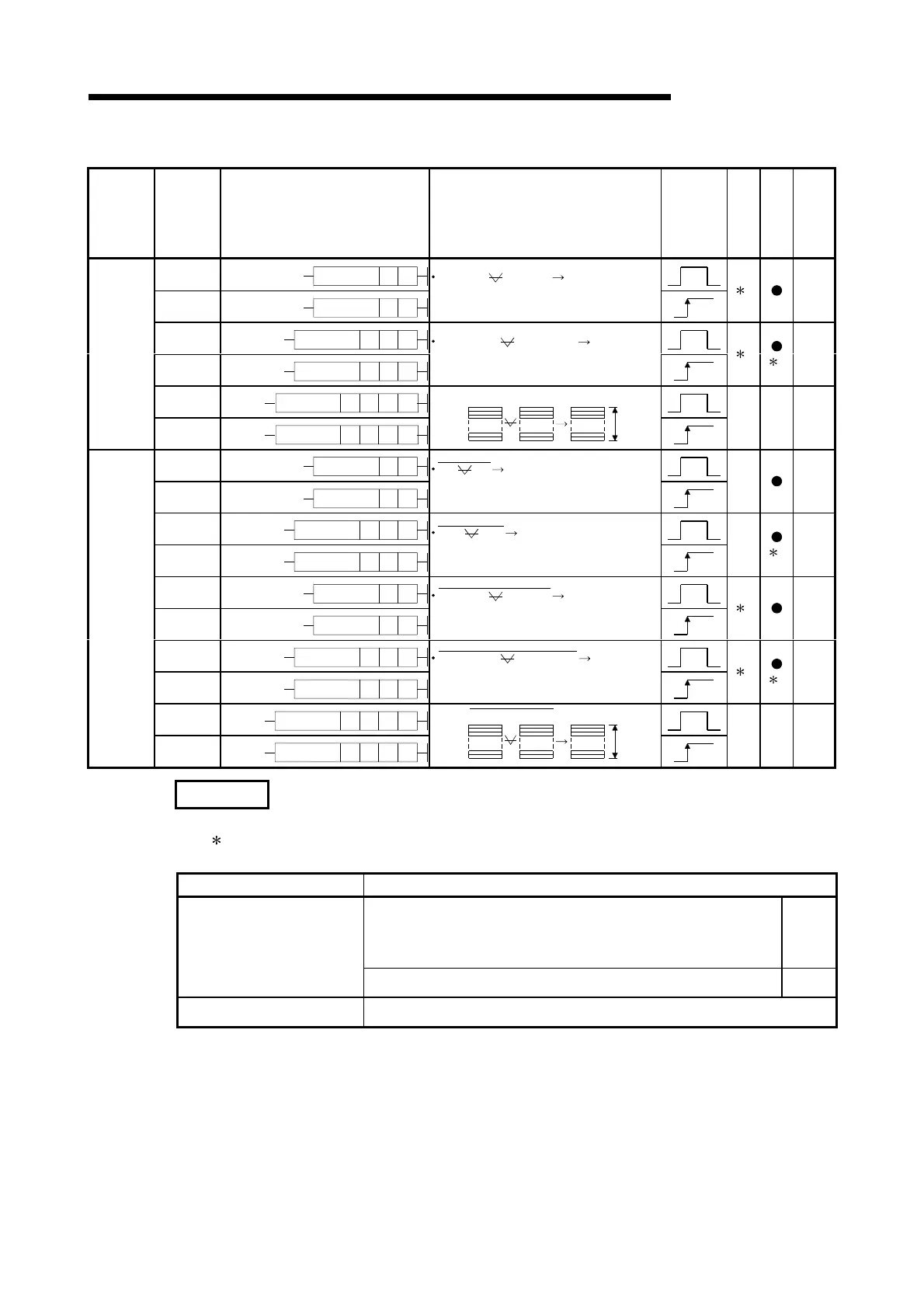

Table 2.18 Logical Operation Instructions (Continued)

Category

Instruction

Symbols

Symbol Processing Details

Execution

Condition

Number of

Basic Steps

Subset

See for

Description

DXOR

DXOR SD

DXORP

DXORP SD

(D+1, D)

(S+1, S) (D+1, D)

1 7-16

DXOR

DXOR S1 S2 D

DXORP

DXORP S1 S2 D

(S1+1, S1)

(S2+1, S2) (D+1, D

2

3

7-18

BKXOR

BKXORP nS1 S2 D

Exclusive

OR

BKXORP

BKXORP nS1 S2 D

(S1)

(S2) (D)

n

57-20

WXNR

WXNR DS

WXNRP

WXNRP DS

(D)

(S)

(D)

3 7-22

WXNR

WXNR S1 S2 D

WXNRP

WXNRP S1 S2 D

(S1)

(S2)

(D)

4

3

7-26

DXNR

DXNR DS

DXNRP

DXNRP DS

(D+1, D)

(S+1, S) (D+1, D

1 7-22

DXNR

DXNR S1 S2 D

DXNRP

DXNRP S1 S2 D

(S2+1, S2) (D+1, D)

(S1+1, S1)

2

3

7-26

BKXNR

BKXNR nS1

S2 D

NON

exclusive

logical sum

BKXNRP

BKXNRP nS1 S2 D

(S1)

(S2) (D)

n

57-28

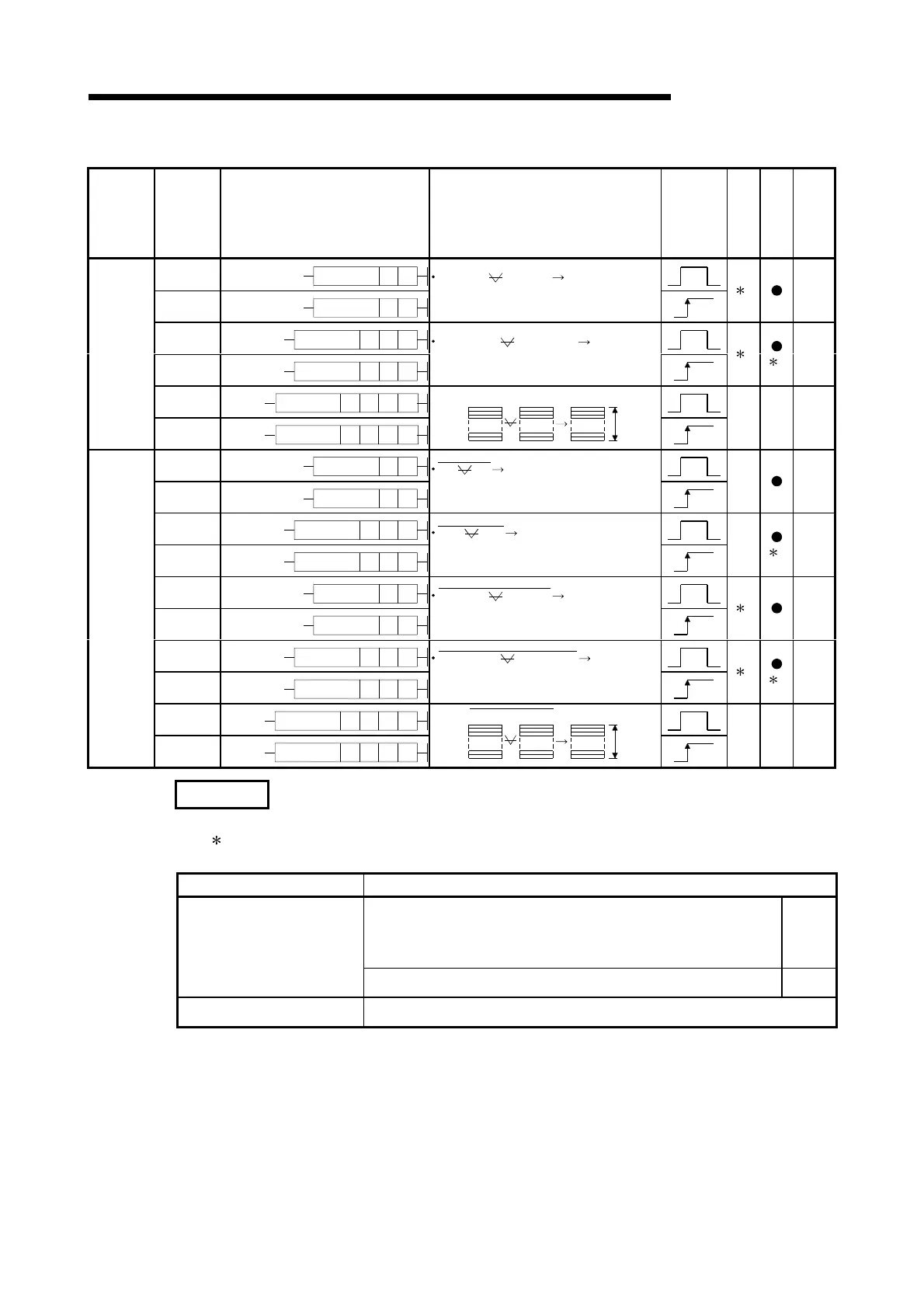

REMARK

1) 1:The number of steps may vary depending on the device and type of CPU module being

used.

Component Nomber of basic steps

(1) When using the following devices only

• Word device : Internal device (except for file register ZR)

• Bit device : Devices whose device Nos. are multiples of 16, whose digit

designation is K8, and which use no index modification.

• Constant : No limitations

Note 1)

5

High Performance model QCPU

Process CPU

(2) When using devices other than (1)

Note 2)

3

Basic model QCPU

QnCPU

3 Note 2)

Note 1:With High Performance module QCPU, (1) requires more number of steps, while it can

process the steps faster, as compared with (2).

Note 2:The number of steps may increase due to the conditions described in Section 3.8.

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...