5 - 5 5 - 5

MELSEC-Q/QnA

5 SEQUENCE INSTRUCTIONS

High Performance

QnA Q4AR

Basic

QCPU

PLC CPU

Process CPU

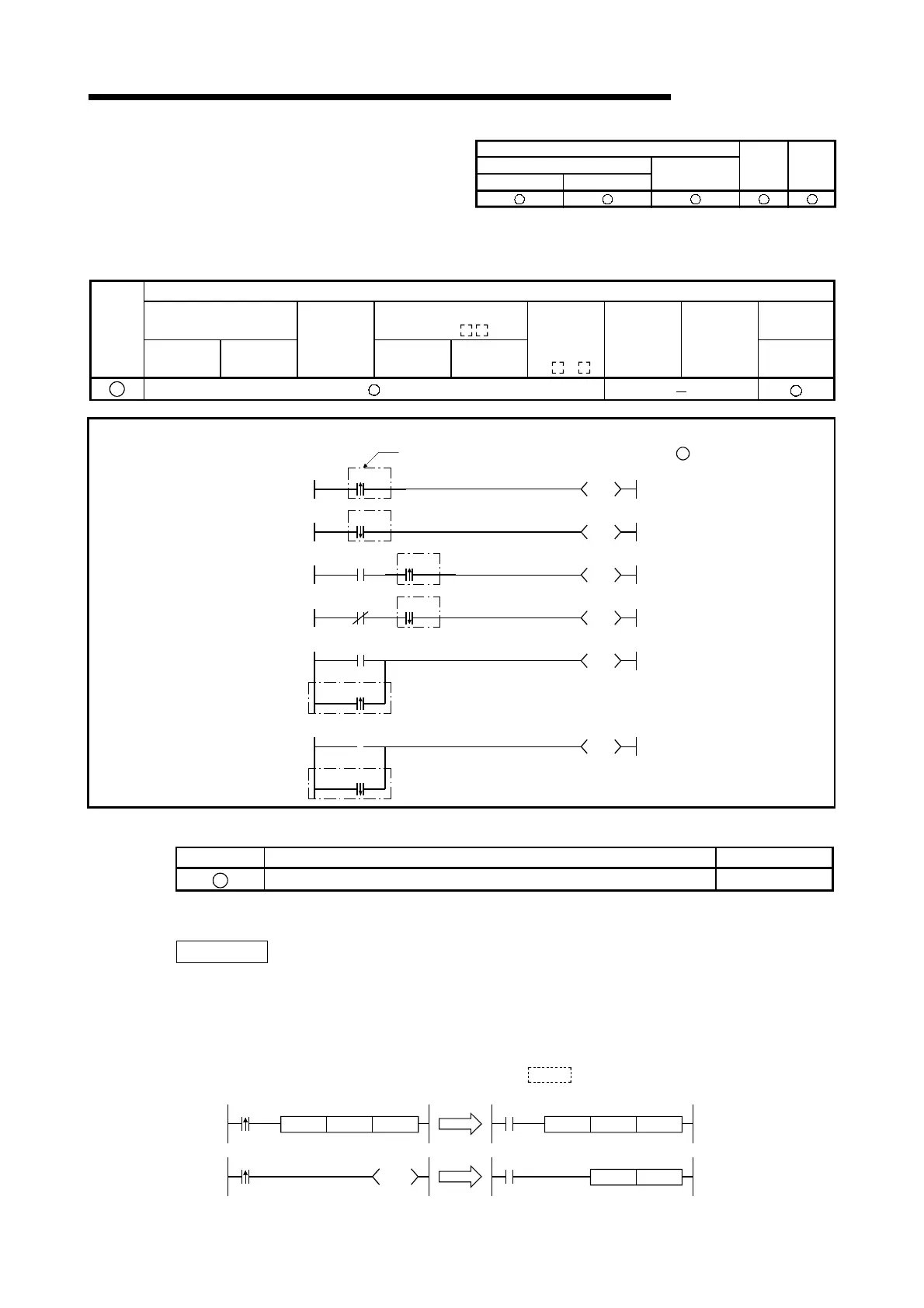

5.1.2 Pulse operation start, pulse series connection, pulse parallel connection

(LDP, LDF, ANDP, ANDF, ORP, ORF)

Usable Devices

Internal Devices

(System, User)

MELSECNET/10(H)

Direct J

\

Other

Set

Data

Bit Word

File

Register

Bit Word

Special

Function

Module

U

\G

Index

Register

Zn

Constant

K, H

DX

S

[Instruction Symbol] [Execution Condition]

X1/D0.1

X1/D0.1

Bit device number/Bit designation of word device ( )

X2/D0.2

X2/D0.2

X3/D0.3

X3/D0.3

LDP

LDF

ORD

ANDP

ANDF

ORF

S

[Set Data]

Set Data Meaning Data Type

S

Devices used as contacts Bit

[Functions]

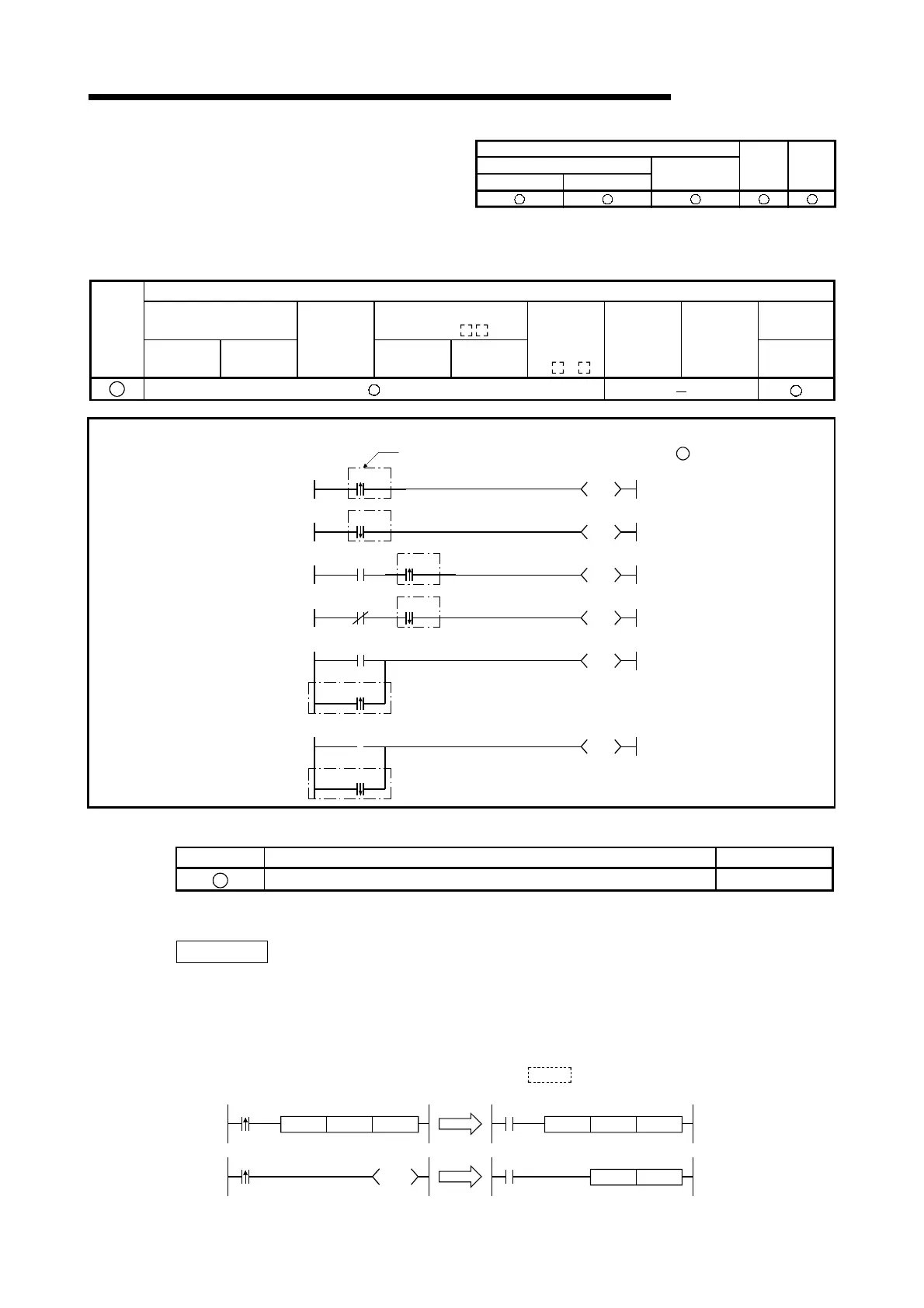

LDP, LDF

(1) LDP is the leading edge pulse operation start instruction, and is ON only at the leading edge of

the designated bit device (when it goes from OFF to ON).

If a word device has been designated, it is ON only when the designated bit changes from 0 to

1.

In cases where there is only an LDP instruction, it acts identically to instructions for the

creation of a pulse that are executed during ON(

P).

X0

D0K0MOV

M0

X0

A ladder using an LDP instruction

X0

D0

K0MOVP

X0

A ladder not using an LDP instruction

M0PLS

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com

Loading...

Loading...