2.3 Terminal unit, IC-215

2-13

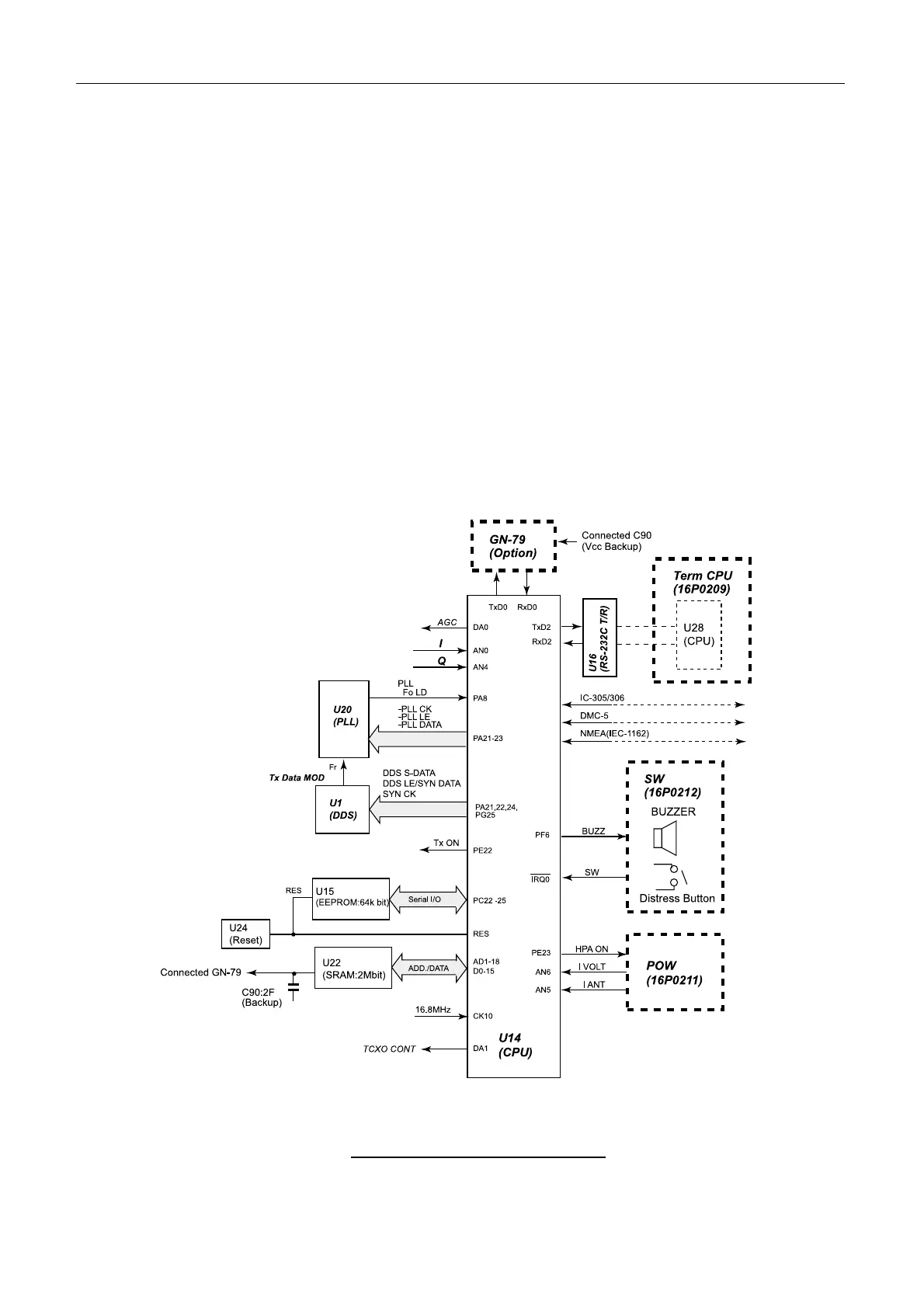

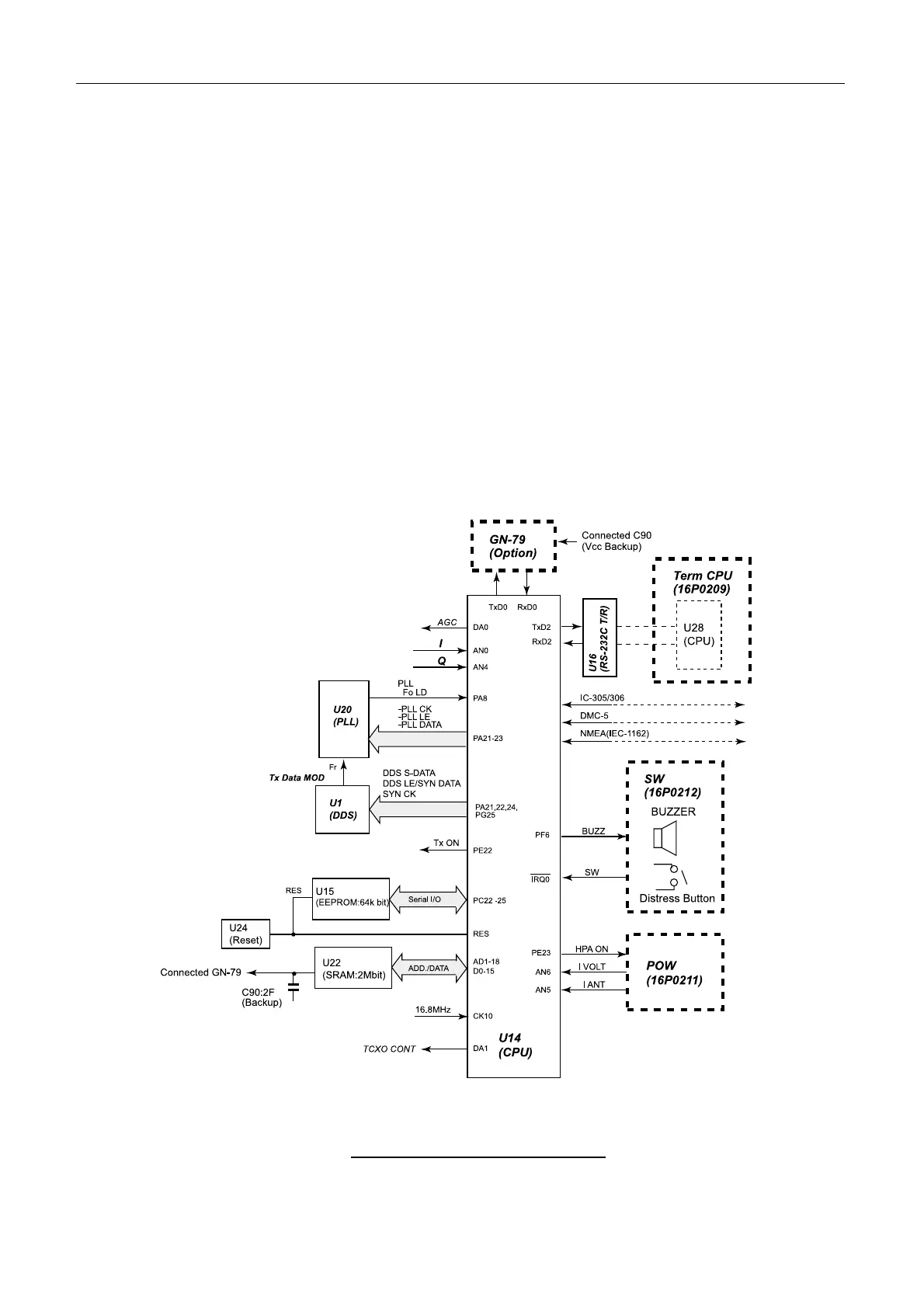

3) CPU

CPU, HD64F7065 is 32 bit single tip microcomputer with DSP function. It consists of ROM

(256 kbyte), RAM (8 kbyte), A/D (8 channels), D/A (2 channels), Timer (8 channels),

watch-dog timer (1 channel) and Serial communication I/F (3 channels).

RF CON/CPU board communicates with TERM CPU board by TD and RD signals which

are I/F of RS-232C.

- Controlling communication protocol of Inmarsat C.

- TX/RX Signal processing - Changing TX and RX circuit

- AGC controlling - Controlling PLL and DDS circuit

- Communicating with TERM CPU - Handling of NMEA data

- Controlling the IC-305 and the IC-306

- Monitoring SYN, V CHK and I ANT signals

Fig.2.3.10 shows the CPU connecting signal.

Fig.2.3.10 CPU connecting signal

Loading...

Loading...