306

Explanations of PLC Setup Settings Section 7-2

Forced Status Hold Bit at

Startup

The Forced Status Hold Bit (A50013) can be turned ON to retain the forced

status of all bits that have been force-set or force-reset when the CPU Unit’s

operating mode is switched between PROGRAM mode and RUN/MONITOR

mode. When the PLC is turned on, the Forced Status Hold Bit itself will be

cleared (OFF) unless it is protected with this PLC Setup setting.

If the Forced Status Hold Bit at Startup setting is ON, the status of the Forced

Status Hold Bit will be protected when the PLC is turned on. If this setting is

ON and the Forced Status Hold BIt itself is ON, all force-set and force-reset

bits will retain their forced status when the PLC is turned on.

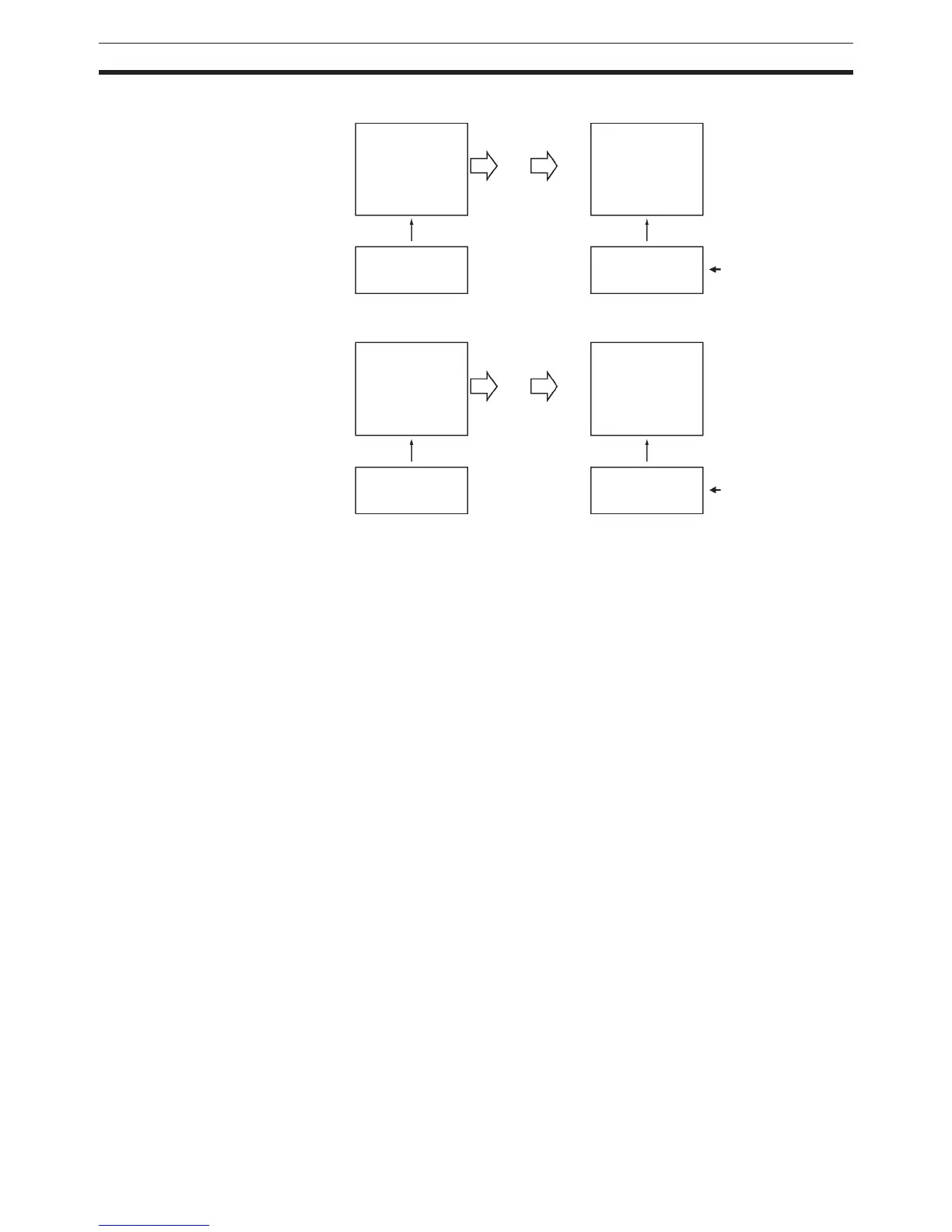

OFF (0): IOM Hold Bit cleared at start-up

Non-retained parts

of I/O memory

Non-retained parts

of I/O memory:

Cleared

Power

OFF

Power

ON

Power

OFF

Power

ON

Mode switch Retained Power on

Not retained

IOM Hold Bit: 1

(ON)

IOM Hold Bit: 0

(OFF)

Not retained when

power is turned ON.

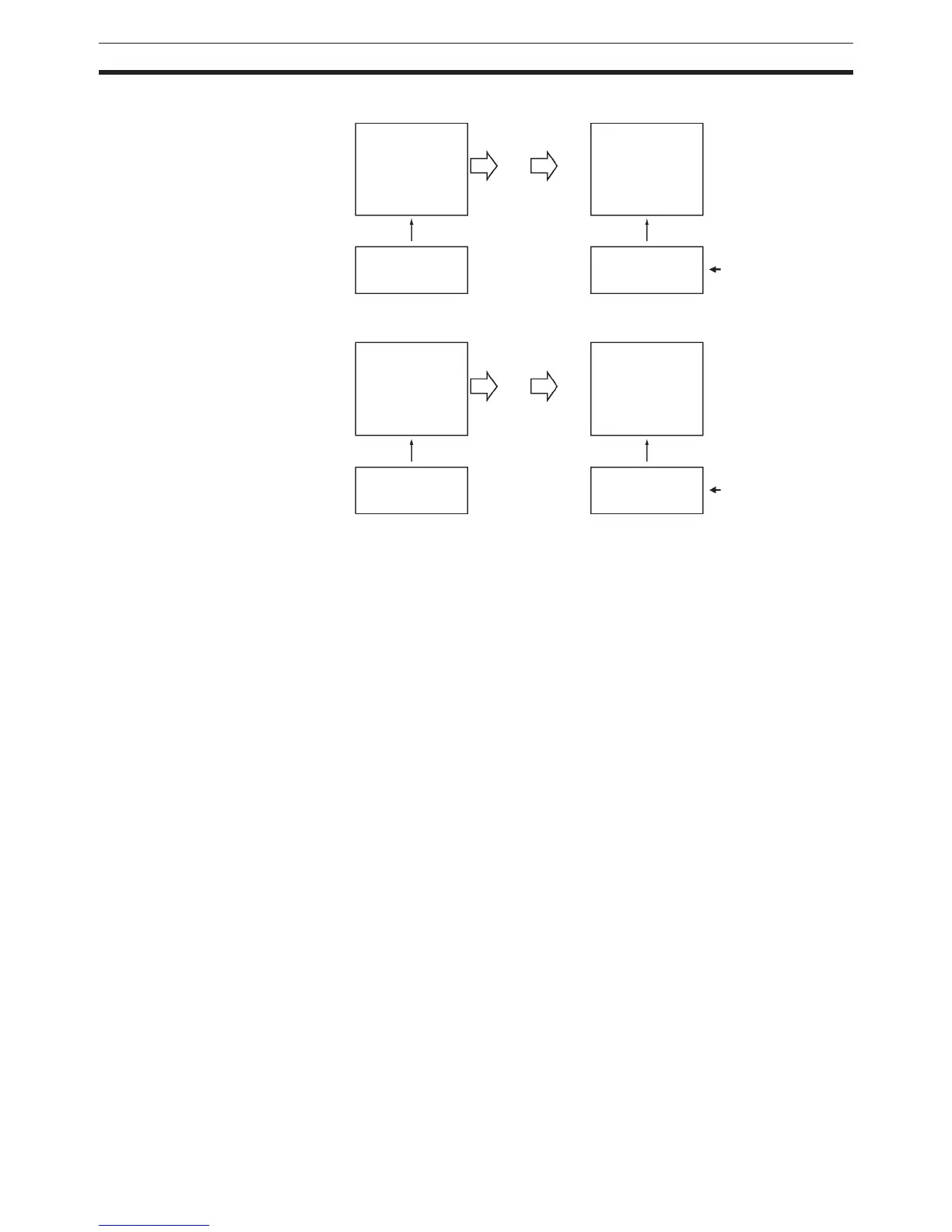

Non-retained parts

of I/O memory

Non-retained parts

of I/O memory:

Retained

Power on Retained

RetainedMode switch

IOM Hold Bit: 1

(ON)

IOM Hold Bit: 1

(ON)

Retained when

power is turned ON.

ON (1): IOM Hold Bit protected at start-up

Loading...

Loading...