217

High-speed Counters Section 5-2

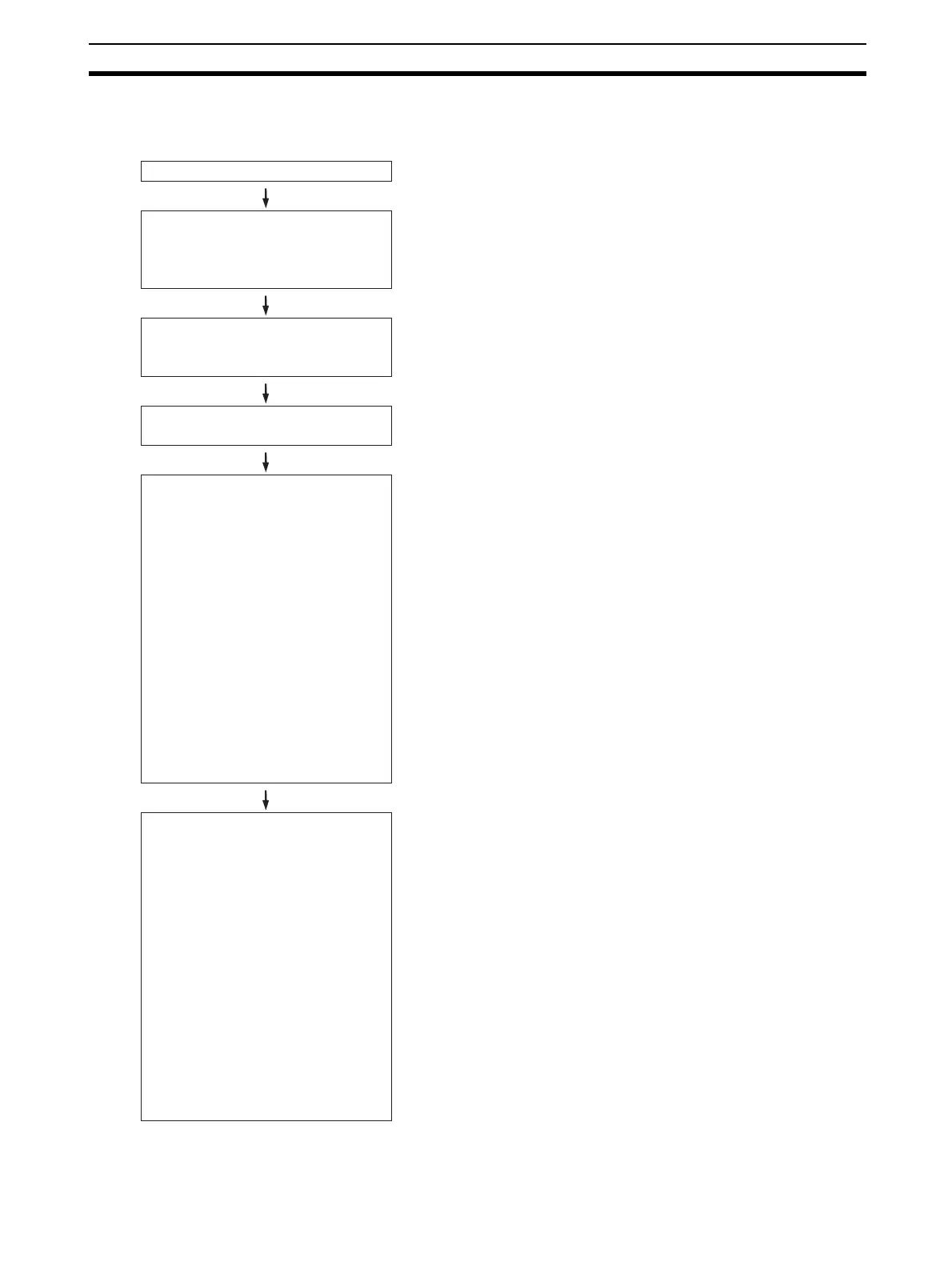

5-2-3 Procedure

Select high-speed counter 0 to 3.

Select the pulse input method, reset

method, and counting range.

Select the kind of interrupt (if any).

Wire inputs.

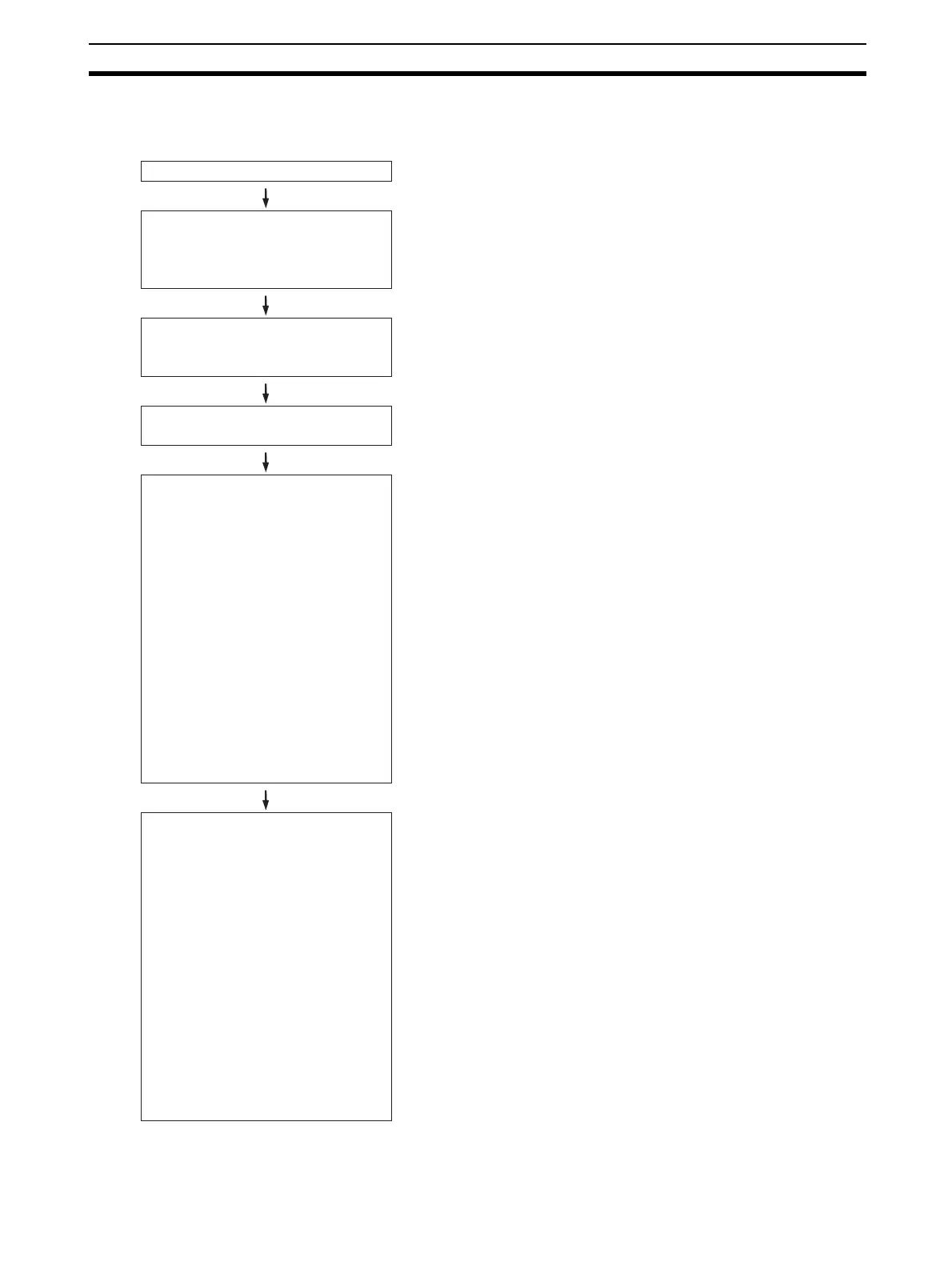

PLC Setup settings

Ladder program

• Pulse input methods: Differential phase (4x), Pulse +

direction, Up/Down, or Increment

• Reset methods: Phase-Z + Software reset, Software

reset, Phase-Z + Software reset (continuing comparing),

Software reset (continuing comparing)

• Counting ranges: Linear mode or Ring mode

• Enable/disable interrupts

• Target value comparison interrupt

• Range comparison interrupt

• Connect to the terminals (24 VDC input or line-

driver)

• High-speed Counters 0 to 3 Enable/Disable:

• High-speed Counters 0 to 3Pulse Input Mode:

Differential phase (4x)

Pulse + direction

Up/Down

Increment

• High-speed Counters 0 to 3 Reset Method:

Phase-Z + Software reset, Software reset, Phase-Z + Software

reset (continuing comparing), Software reset (continuing

comparing)

• High-speed Counters 0 to 3 Counting Mode:

Linear mode

Ring mode

• Program the interrupt task (with any interrupt number between 0

and 255) to be executed when using a target value comparison

or range comparison interrupts.

• Register a target value comparison table and start the

comparison.

• Register a range comparison table and start the comparison.

• Register a target value comparison table without starting the

comparison.

• Register a range comparison table without starting the

comparison.

• Change the counter PV.

• Start comparison with the registered target value comparison

table or range comparison table.

• Read the high-speed counter PVs, read the status of the high-

speed counter comparison operation, or read the range-

comparison results.

• Turn ON the High-speed Counter Gate Bit to stop counting input

pulses.

• High-speed counters 0 to 3 on X/XA CPU Units and high-speed

counters 2 and 3 on Y CPU Units: 24 VDC input, Response

frequency: 50 kHz for single-phase, 100 kHz for differential phase

• High-speed counters on Y CPU Units: Line-driver input, Response

frequency: 500 kHz for single-phase, 1 MHz for differential phase

Loading...

Loading...