RTL8169

2002/03/27 Rev.1.21

19

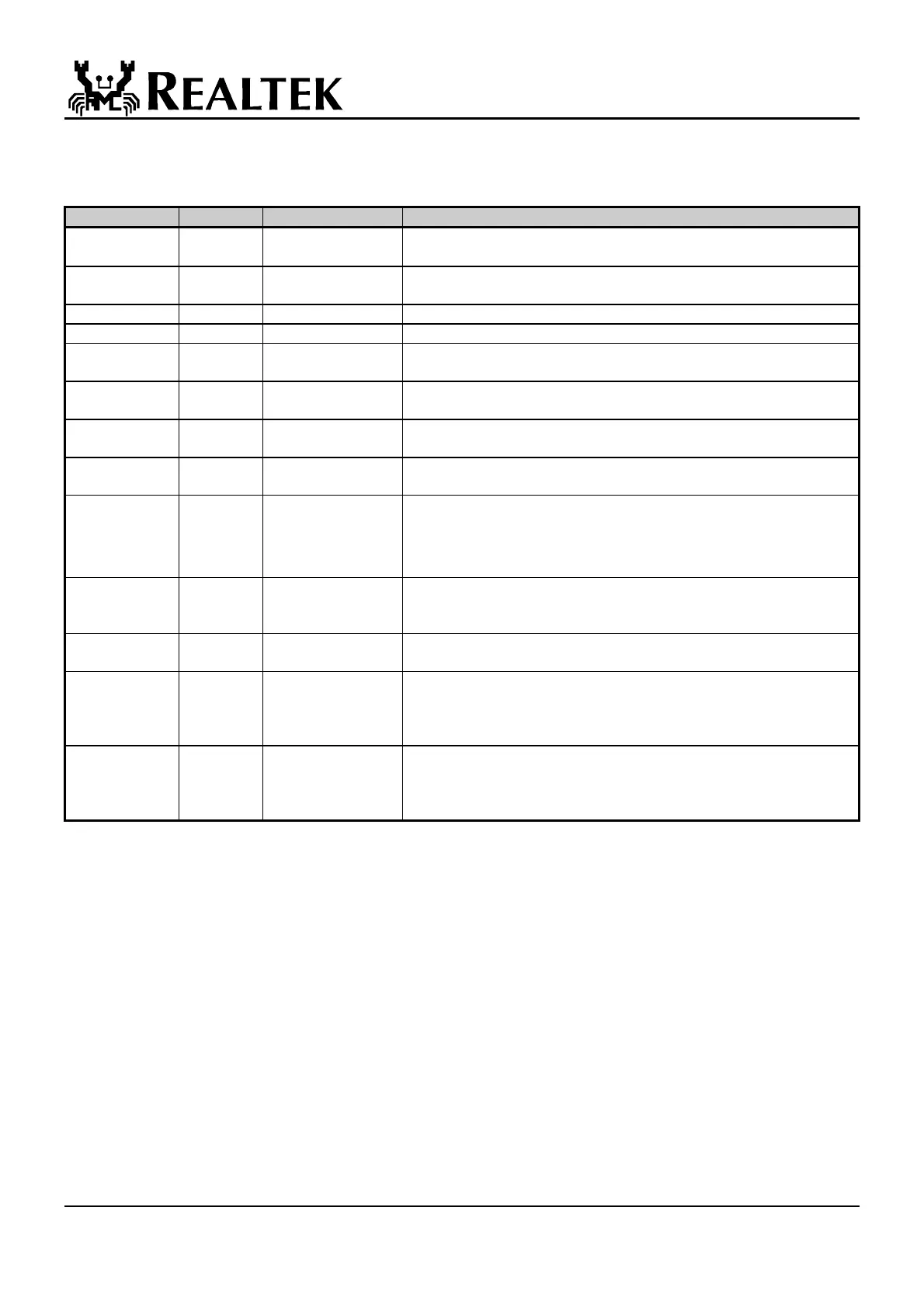

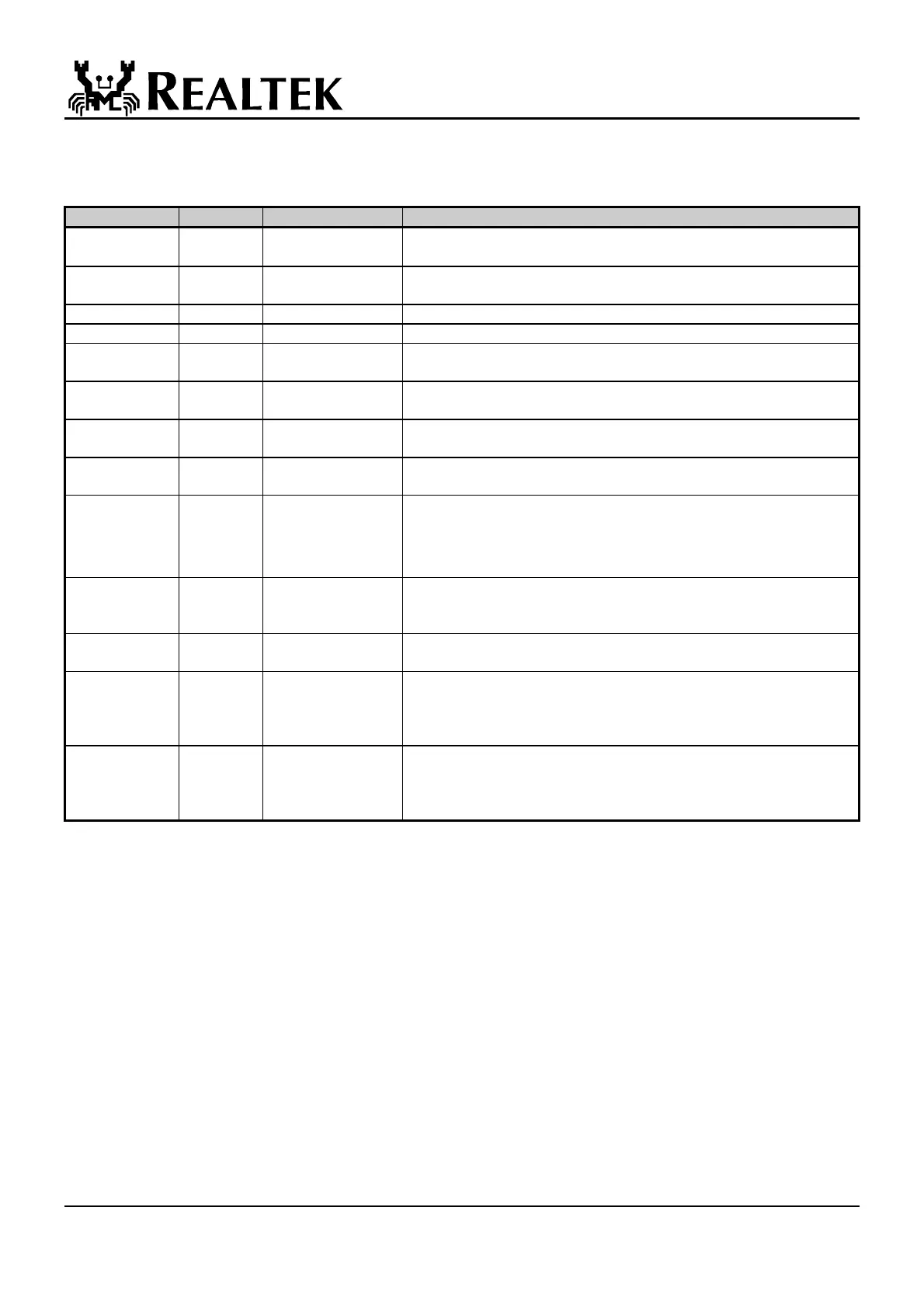

6.7 Interrupt Status

(Offset 003Eh-003Fh, R/W)

Bit R/W Symbol Description

15 R/W SERR

System Error: This bit is set to 1 when the RTL8169 signals a system

error on the PCI bus.

14 R/W TimeOut

Time Out: This bit is set to 1 when the TCTR register reaches the value

of the TimerInt register.

13:10 - -

Reserved

9 - -

Reserved

8 R/W SWInt

Software Interrupt: This bit is set to 1 whenever a ‘1’ is written by

software to FSWInt (bit0, offset D9h, TPPoll register).

7 R/W TDU

Tx Descriptor Unavailable: When set, this bit indicates that the Tx

descriptor is unavailable.

6 R/W FOVW

Rx FIFO Overflow: This bit set to 1 is caused by RDU, poor PCI

performance, or overloaded PCI traffic.

5 R/W PUN/LinkChg

Packet Underrun/Link Change: This bit is set to 1 when CAPR is

written but the Rx buffer is empty, or when link status is changed.

4 R/W RDU

Rx Descriptor Unavailable: When set to 1, this bit indicates that the

Rx descriptor is unavailable.

The MPC (Missed Packet Counter, offset 4Ch-4Fh) indicates the

number of packets discarded after Rx FIFO overflowed.

3 R/W TER

Transmit (Tx) Error: This bit set to 1 indicates that a packet

transmission was aborted, due to excessive collisions, according to the

TXRR's setting in the TCR register.

2 R/W TOK

Transmit (Tx) OK: When set to 1, this bit indicates that a packet

transmission has been completed successfully.

1 R/W RER

Receive (Rx) Error: When set to 1, this bit indicates that a packet has

either a CRC error or a frame alignment error (FAE). A Rx error packet

of CRC error is determined according to the setting of RER8, AER, AR

bits in RCR register (offset 44h-47h).

0 R/W ROK

Receive (Rx) OK: In normal mode, this bit set to 1 indicates the

successful completion of a packet reception. In early mode, this bit set

to 1 indicates that the Rx byte count of the arriving packet exceeds the

early Rx threshold.

Writing 1 to any bit in the ISR will reset that bit.

Loading...

Loading...