RTL8169

2002/03/27 Rev.1.21

35

20h-2Fh -

Reserved

30h-31h CISPointer

Reserved: Do not change this field without Realtek approval.

CIS Pointer.

32h-33h CheckSum

Reserved: Do not change this field without Realtek approval.

Checksum of the EEPROM content.

34h-3Eh -

Reserved: Do not change this field without Realtek approval.

3Fh PXE_Para

Reserved: Do not change this field without Realtek approval.

PXE ROM code parameter.

40h-7Fh VPD_Data

VPD data field: Offset 40h is the start address of the VPD data.

80h-FFh CIS_Data

CIS data field: Offset 80h is the start address of the CIS data. (93C56 only).

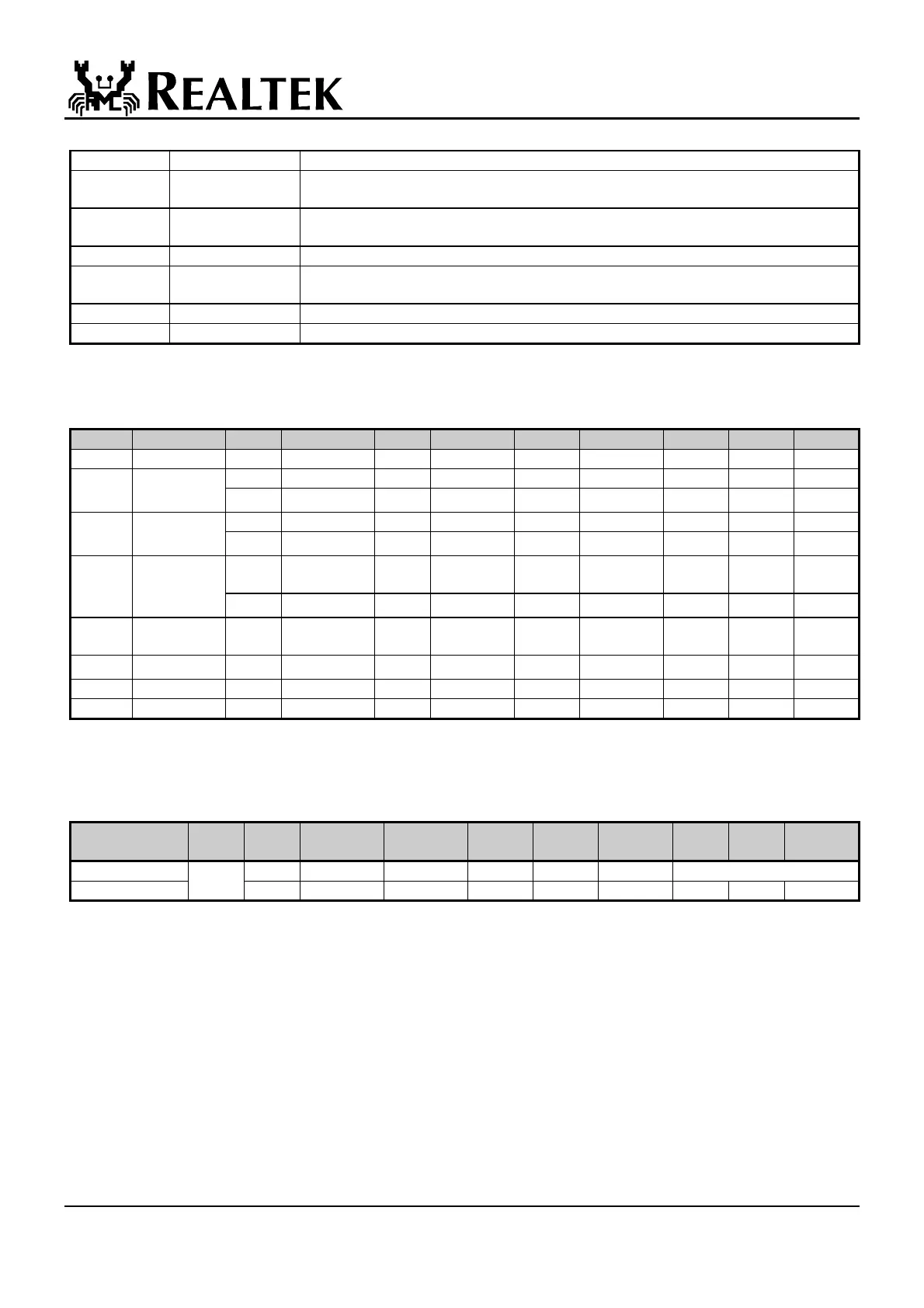

7.1 EEPROM Registers

Offset Name Type Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

00h-05h IDR0 – IDR5 R/W*

51h CONFIG0 R - - - - BS2 BS1 BS0

W

*

- - - - - - - -

52h CONFIG1 R LEDS1 LEDS0 DVRLOAD LWACT MEMMAP IOMAP VPD PMEN

W

*

LEDS1 LEDS0 DVRLOAD LWACT - - VPD PMEN

54h CONFIG3 R GNTDel - Magic LinkUp CardB_En CLKRU

N_En

FuncReg

En

FBtBEn

W

*

- - Magic LinkUp - - - -

55h CONFIG4

R/W

*

RxFIFOAuto

Clr

- - LWPME - LWPTN - -

56h CONFIG5

R/W

*

- - - - - - LANWake PME_STS

6Ch PHYStatus R EnTBI - - - - - - -

E1h C+CR R/W - - - - - - Endian -

* The registers marked with type = 'W

*'

can be written only if bits EEM1=EEM0=1.

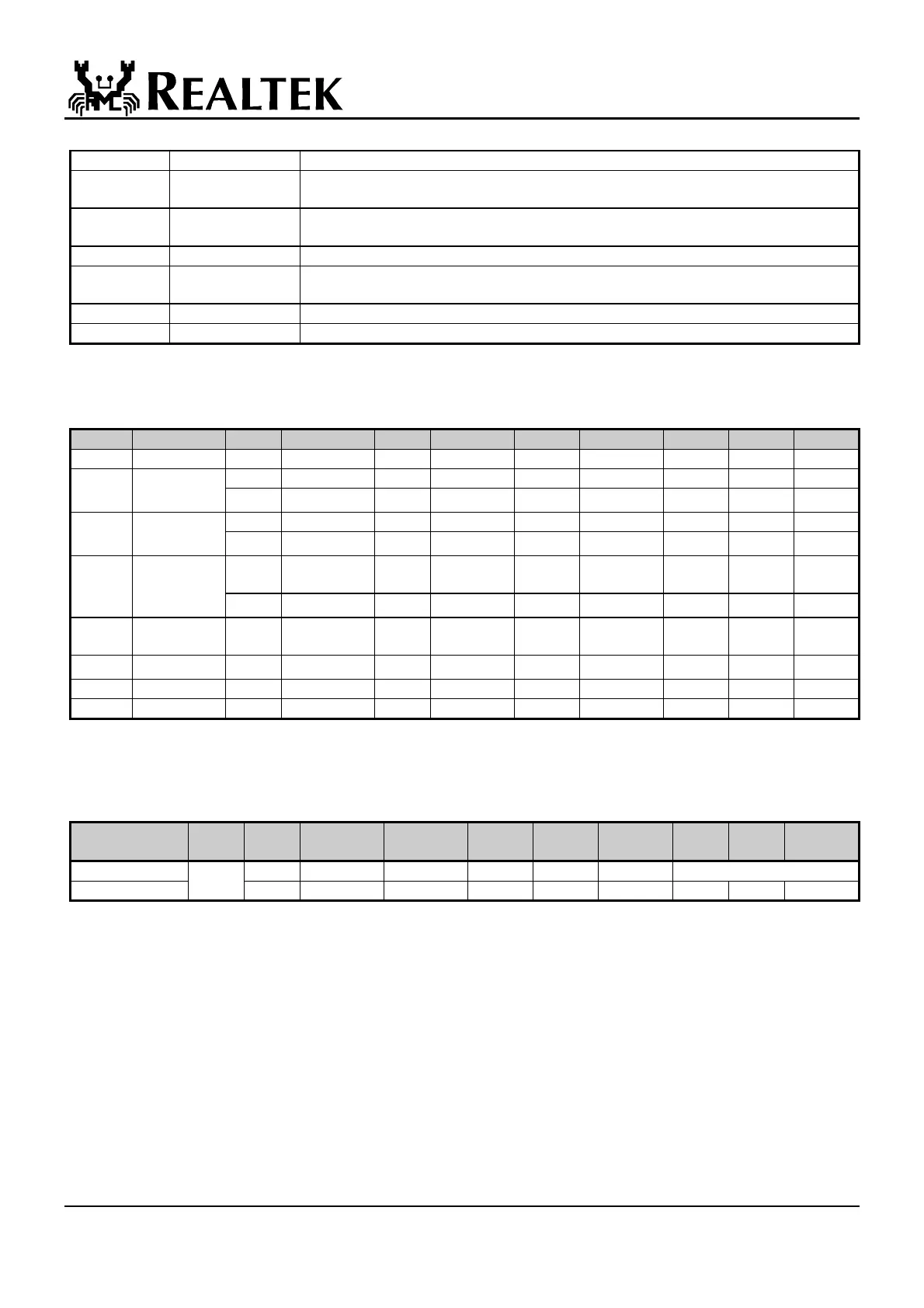

7.2 EEPROM Power Management Registers

Configuration

Space offset

Name Type Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

DEh R Aux_I_b1 Aux_I_b0 DSI Reserved PMECLK Version

DFh

PMC

R PME_D3

cold

PME_D3

hot

PME_D2 PME_D1 PME_D0 D2 D1 Aux_I_b2

Loading...

Loading...