RTL8169

2002/03/27 Rev.1.21

70

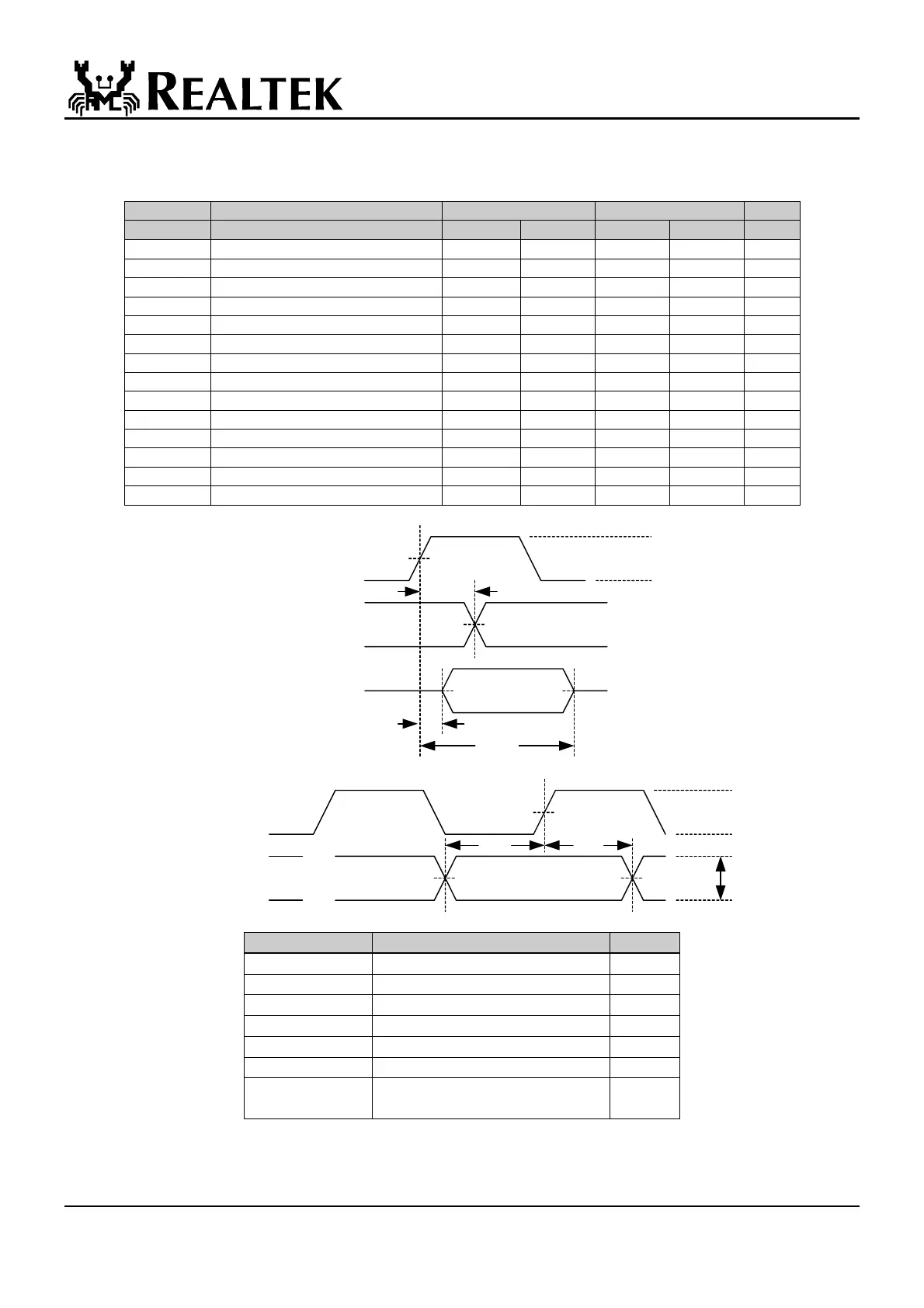

11.3.3 PCI Bus Operation Timing

PCI Bus Timing Parameters

66MHz 33MHz

Symbol Parameter Min Max Min Max Units

T val

CLK to Signal Valid Delay-bused signals

2 6 2 11 ns

T val(ptp)

CLK to Signal Valid Delay-point to point

2 6 2 12 ns

T on

Float to Active Delay

2 2 ns

T off

Active to Float Delay

14 28 ns

T su

Input Setup Time to CLK-bused signals

3 7 ns

T su(ptp)

Input Setup Time to CLK-point to point

5 10 ns

T h

Input Hold Time from CLK

0 0 ns

T rst

Reset active time after power stable

1 1 ms

T rst-clk

Reset active time after CLK STABLE

100 100 us

T rst-off

Reset Active to Output Float delay

40 40 ns

Trrsu

REQB to REQ64B Setup Time

10*Tcyc 10*Tcyc ns

Trrh

RSTB to REQ64B Hold Time

0 50 0 50 ns

T rhfa

RSTB High to First configuration Access

2^25 2^25 clocks

T rhff

RSTB High to First FRAMEB assertion

5 5 clocks

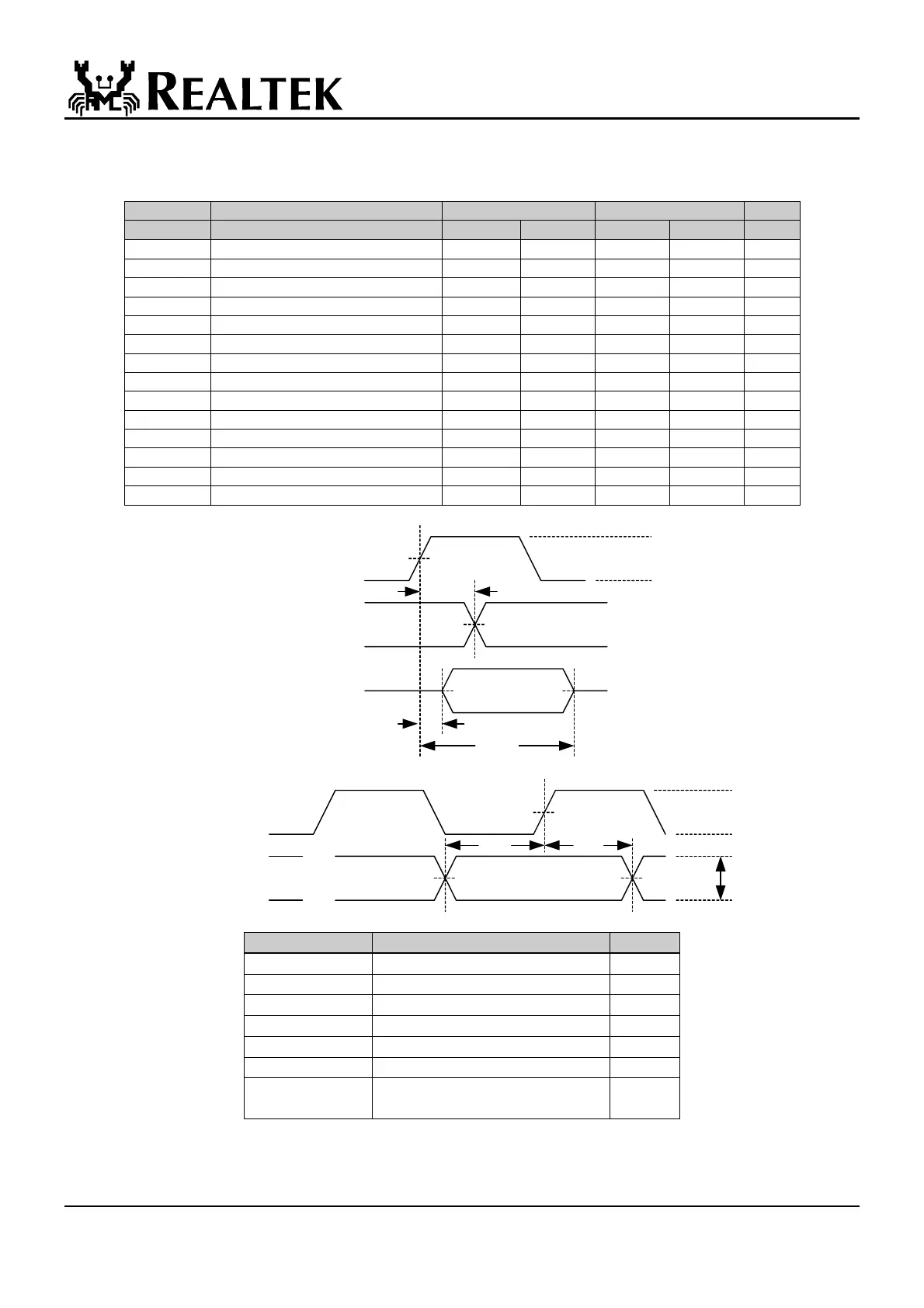

PCI Interface Timing Parameters

CLK

OUTPUT

DELAY

Tri-State

OUTPUT

V_th

V_tl

V_test

V_trise, V_tfall

T_off

T_val

T_on

V_testV_test

Output Timing Measurement Condition

CLK

INPUT

V_th

V_tl

V_test

V_test

T_su

V_th

V_tl

T_h

V_test inputs valid V_max

Input Timing Measurement Conditions

Symbol Level Units

Vth

0.6Vcc V

Vtf

0.2Vcc V

Vtest

0.4Vcc V

Vtrise

0.285Vcc V

Vtfall

0.615Vcc V

Vmax

0.4Vcc V

Input Signal

Edge Rate

1 V/ns

Measurement Condition Parameters

Loading...

Loading...