RTL8169

2002/03/27 Rev.1.21

30

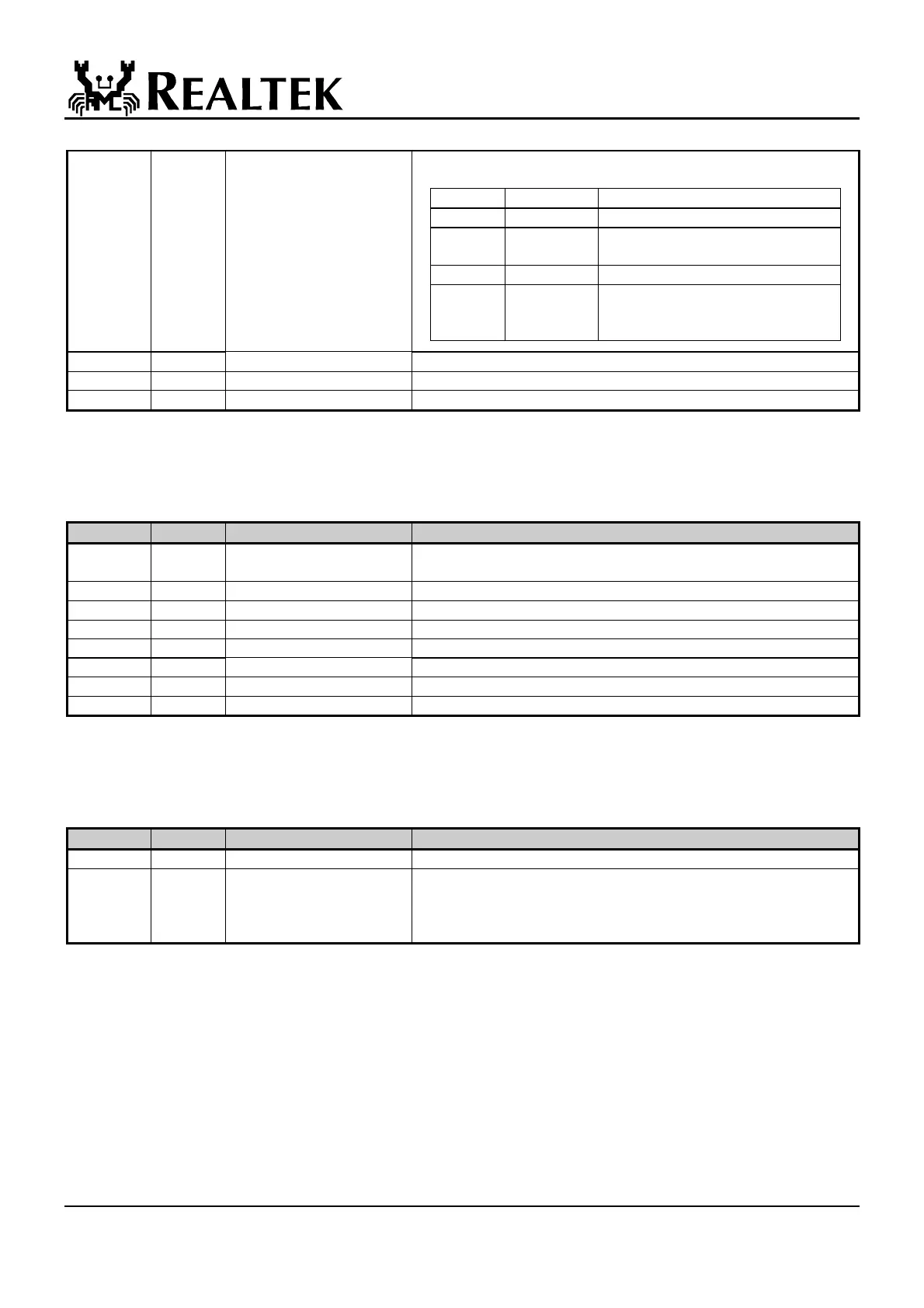

Asymmetric Pause: When this bit is set, the value of bit7 (Pause)

indicates the direction that PAUSE frames are supported by the link partner.

PS1 PS2 Capability

0 0 No Pause.

0 1 Asymmetric PAUSE toward link

partner.

1 0 Symmetric PAUSE.

1 1 Both symmetric PAUSE and

asymmetric PAUSE toward local

device.

8:7 R PS2(ASM_DIR),

PS1(PAUSE)

6 R HalfDup

Half Duplex: When set, the link partner supports half duplex.

5 R FullDup

Full Duplex: When set, the link partner supports full duplex.

4:0 - -

Reserved

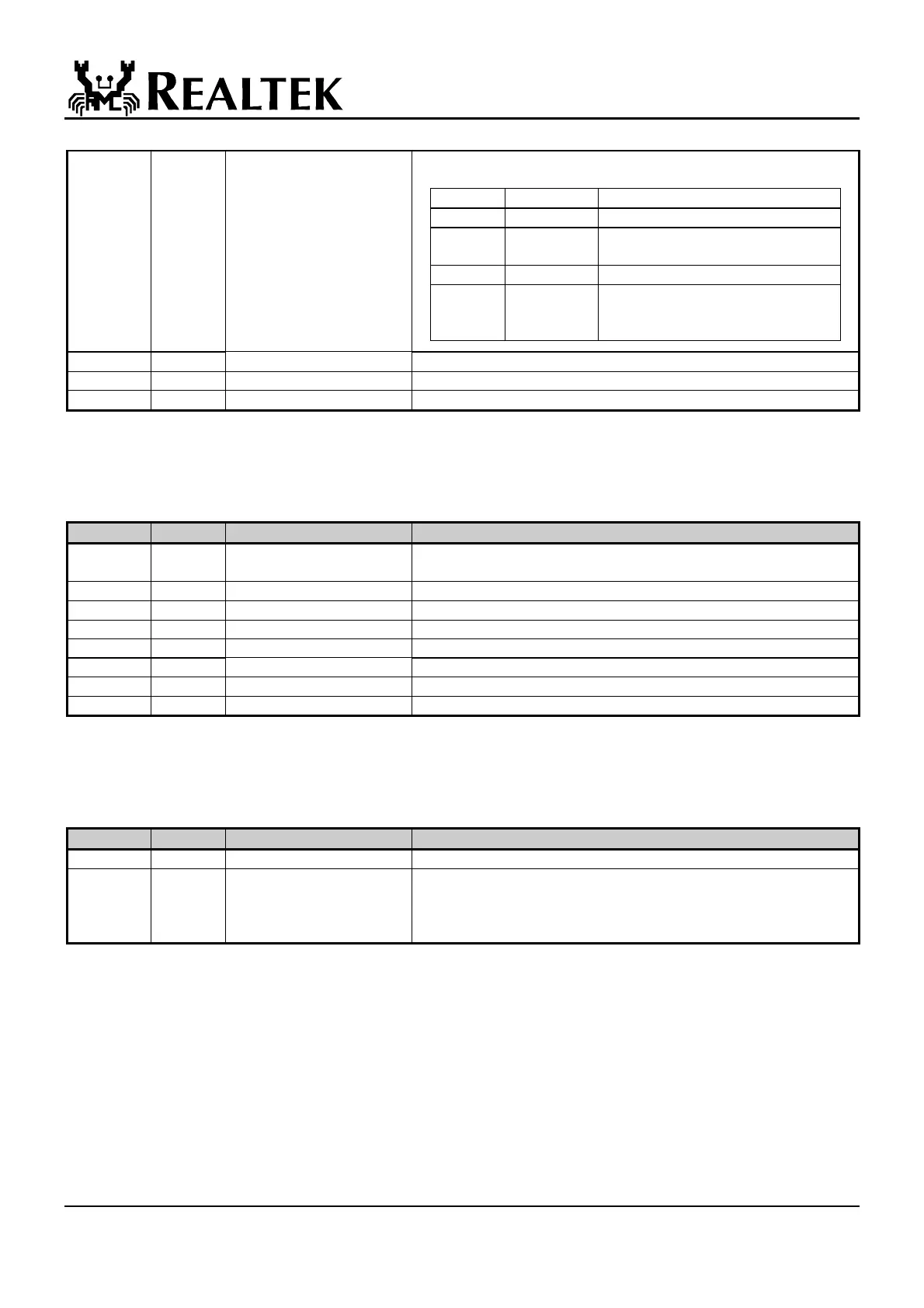

6.22 PHYStatus: PHY(GMII or TBI) Status

(Offset 006Ch, R)

Bit R/W Symbol Description

7 R EnTBI

TBI Enable: This bit is autoloaded from the EEPROM.

1: TBI mode, 0: GMII(MII) mode.

6 R TxFlow

Transmit Flow Control: 1: Enabled, 0: Disabled.

5 R RxFlow

Receive Flow Control: 1: Enabled, 0: Disabled.

4 R 1000MF Link speed is 1000Mbps and in full-duplex. (GMII mode only)

3 R 100M Link speed is 100Mbps. (GMII or MII mode only)

2 R 10M Link speed is 10Mbps. (GMII or MII mode only)

1 R LinkSts Link Status. 1: Link Ok, 0: No Link.

0 R FullDup

Full-Duplex Status: 1: Full-duplex mode, 0: Half-duplex mode.

- MII registers polling cycle: 320ns * (32 MDC clock + 32 MDC clock) * 6 registers

6.23 RMS: Receive (Rx) Packet Maximum Size

(Offset 00DAh-00DBh, R)

Bit R/W Symbol Description

15:14 - -

Reserved

13:0 R/W RMS

Rx packet Maximum Size:

i. This register should be always set to a value other than 0, in

order to receive packets.

ii. The maximum size supported is 2

14

-1, i.e., 16K-1 bytes.

Loading...

Loading...