RTL8169

2002/03/27 Rev.1.21

37

8.1.4 64-Bit Data Operation

The RTL8169 samples the REQ64B pin at PCI RSTB deasserted to determine if the bus is 64-bit capable.

8.1.5 64-Bit Addressing

The RTL8169 supports 64-bit addressing (Dual Address Cycle, DAC) as a bus master for transferring descriptor and packet data

information. The DAC mode can be enabled or disabled through software. The RTL8169 only supports 32-bit addressing as a

target.

8.2 Bus Operation

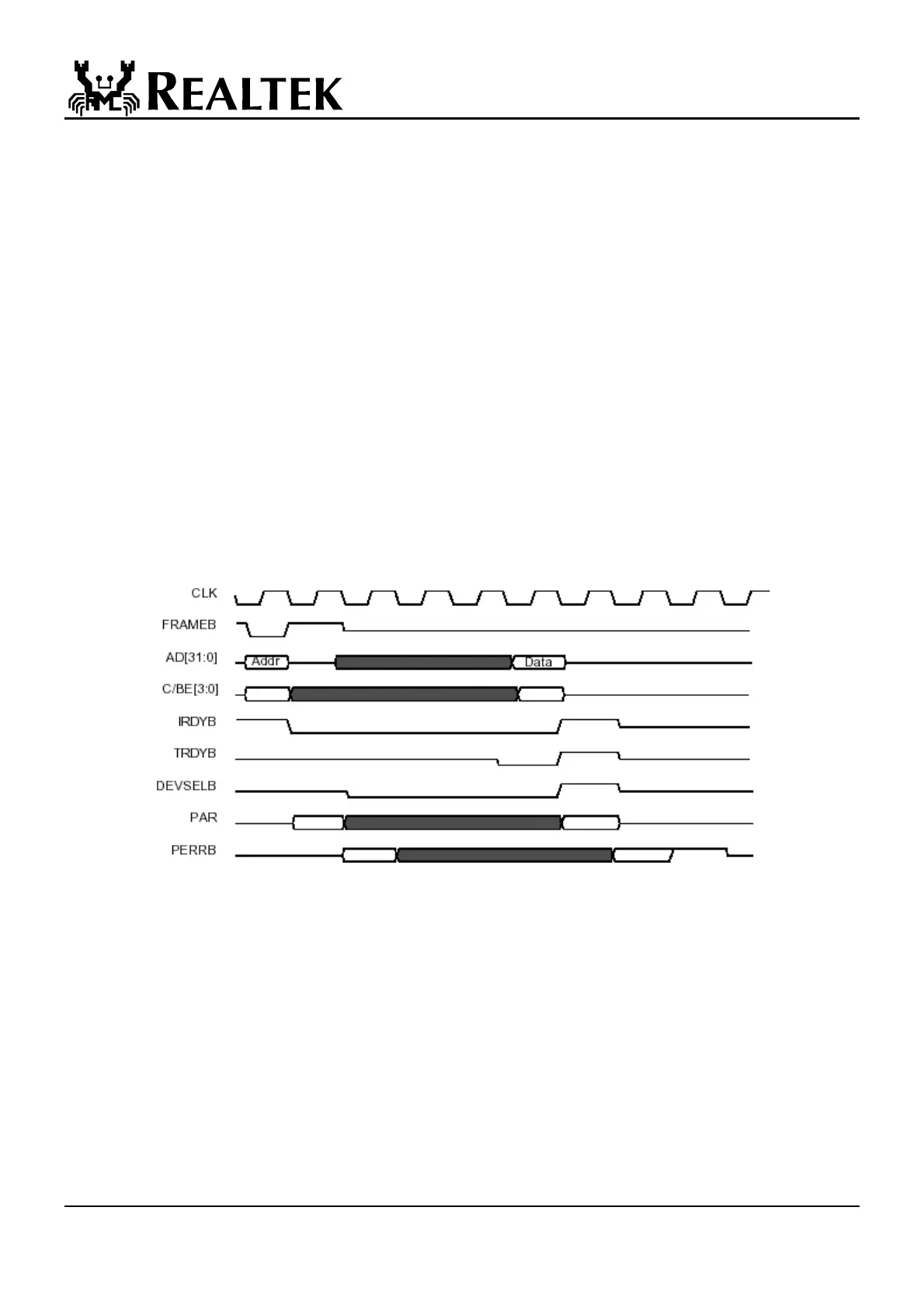

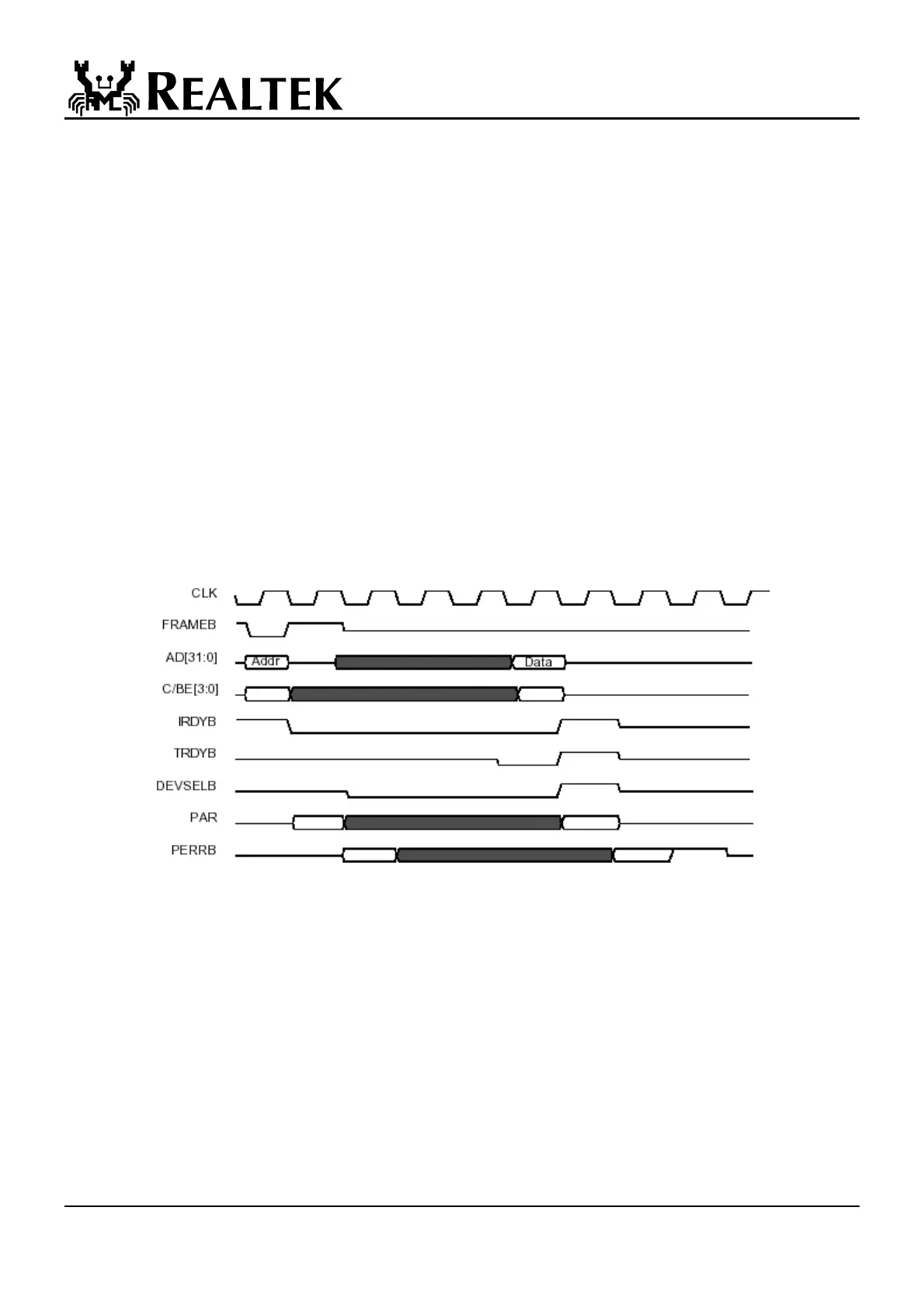

8.2.1 Target Read

A Target Read operation starts with the system generating FRAMEB, Address, and either an IO read (0010b) or Memory Read

(0110b) command. If the 32-bit address on the address bus matches the IO address range specified in IOAR (for I/O reads) or the

memory address range specified in MEM (for memory reads), the RTL8169 will generate DEVSELB 2 clock cycles later

(medium speed). The system must tri-state the Address bus, and convert the C/BE bus to byte enables, after the address cycle. On

the 2nd cycle after the assertion of DEVSELB, all 32-bits of data and TRDYB will become valid. If IRDYB is asserted at that

time, TRDYB will be forced HIGH on the next clock for 1 cycle, and then tri-stated.

If FRAMEB is asserted beyond the assertion of IRDYB, the RTL8169 will still make data available as described above, but will

also issue a Disconnect. That is, it will assert the STOPB signal with TRDYB. STOPB will remain asserted until FRAMEB is

detected as deasserted.

Target Read Operation

Loading...

Loading...