RTL8169

2002/03/27 Rev.1.21

45

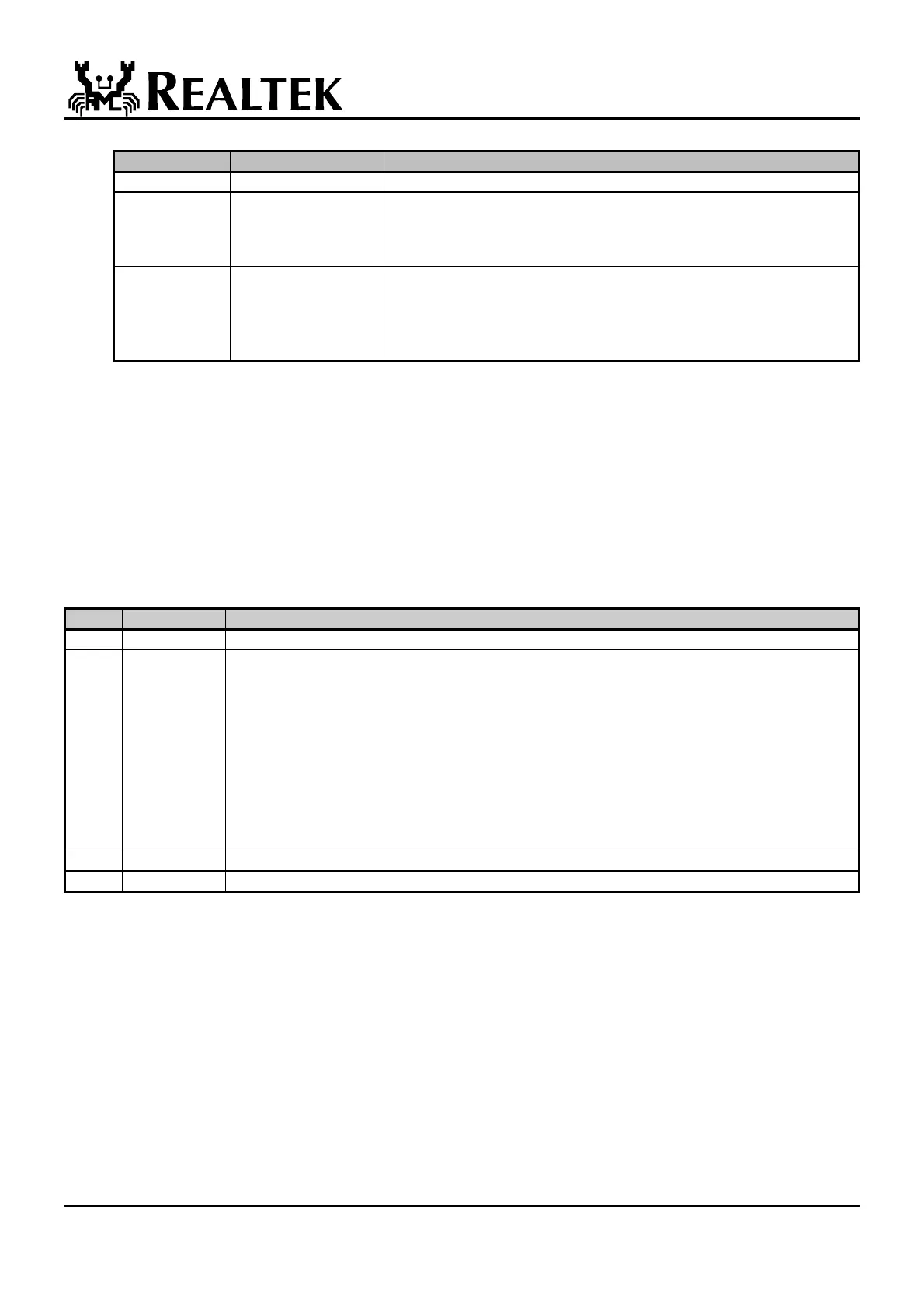

Bit2-0 Space Type Address Space Offset Values

0 Configuration space Not supported.

X; 1≤X≤6

Memory space

0h≤value≤FFFF FFF8h. This is the offset into the memory address space

governed by Base Address Register X. Adding this value to the value in the

Base Address Register gives the location of the start of the CIS. For the

RTL8169, the value is 100h.

7 Expansion ROM

0≤image number≤Fh, 0h≤value≤0FFF FFF8h. This is the offset into the

expansion ROM address space governed by the Expansion ROM Base

Register. The image number is in the uppermost nibble of the CISPtr

register. The value consists of the remaining bytes. For the RTL8169, the

image number is 0h.

This read-only register points to where the CIS begins, in one of the following spaces:

i. Memory Space – The CIS may be in any of the memory spaces from offset 100h and up after being auto-loaded from

93C56. The CIS is stored in 93C56 EEPROM physically from offset 80h-FFh.

ii. Expansion ROM space – The CIS is stored in expansion ROM physically within the 128KB max.

SVID: Subsystem Vendor ID. This field will be set to a value corresponding to PCI Subsystem Vendor ID in the external

EEPROM. If there is no EEPROM, this field will default to a value of 10ECh which is Realtek Semiconductor's PCI

Subsystem Vendor ID.

SMID: Subsystem ID. This field will be set to value corresponding to PCI Subsystem ID in the external EEPROM. If there is no

EEPROM, this field will default to a value of 8129h.

BMAR: This register specifies the base memory address for memory accesses to the RTL8169 operational registers. This

register must be initialized prior to accessing any of the RTL8169's register with memory access.

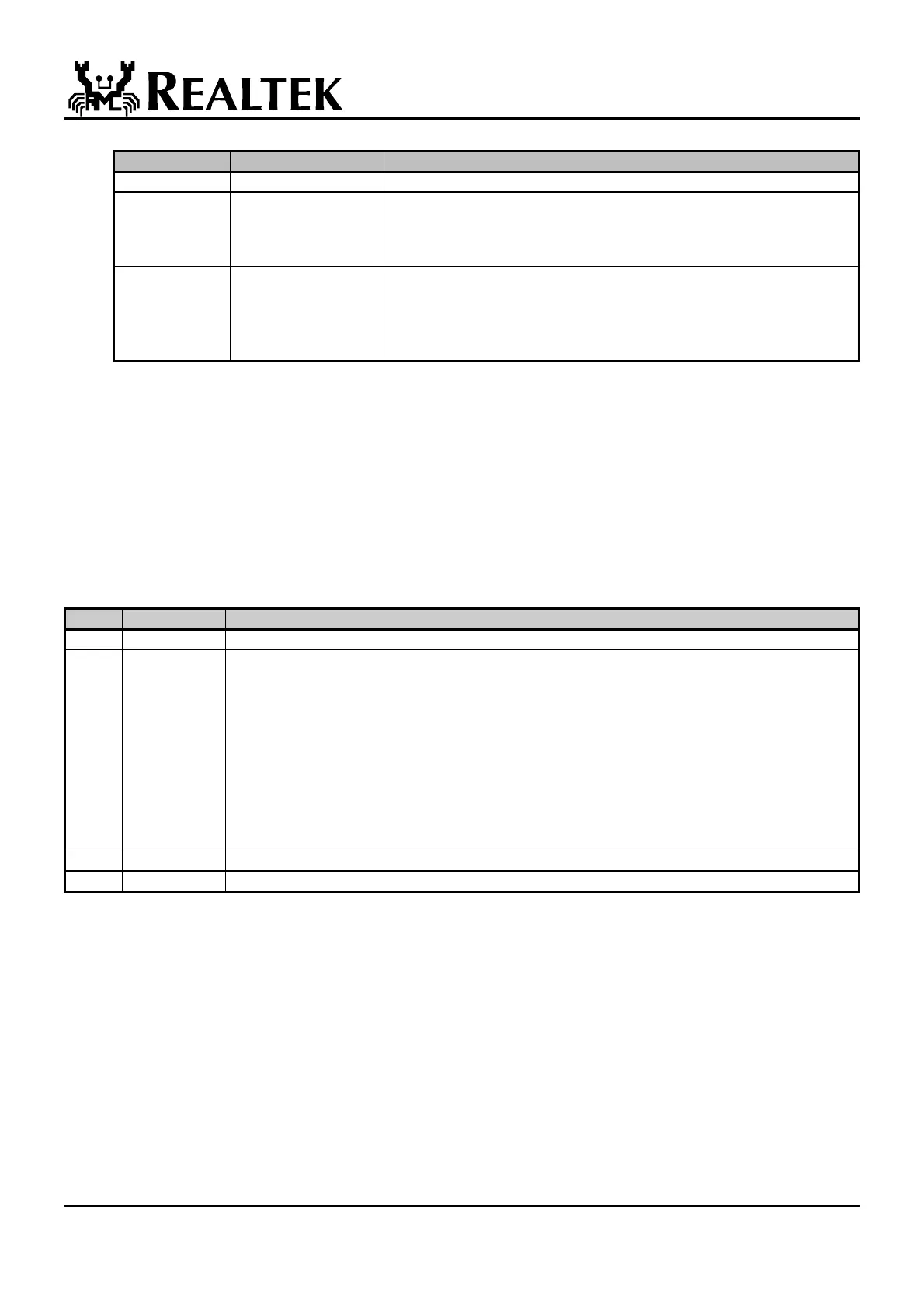

Bit Symbol Description

31:18 BMAR31-18

Boot ROM Base Address

17:11 ROMSIZE

Boot ROM Size: These bits indicate how many Boot ROM spaces to be supported. The Relationship

between Config 0 <BS2:0> and BMAR17-11 is as follows:

BS2 BS1 BS0 Description

0 0 0 No Boot ROM, BROMEN=0 (R)

0 0 1 8K Boot ROM, BROMEN (R/W), BMAR12-11 = 0 (R), BMAR17-13 (R/W)

0 1 0 16K Boot ROM, BROMEN (R/W), BMAR13-11 = 0 (R), BMAR17-14 (R/W)

0 1 1 32K Boot ROM, BROMEN (R/W), BMAR14-11 = 0 (R), BMAR17-15 (R/W)

1 0 0 64K Boot ROM, BROMEN (R/W), BMAR15-11 = 0 (R), BMAR17-16 (R/W)

1 0 1 128K Boot ROM, BROMEN(R/W), BMAR16-11=0 (R), BMAR17 (R/W)

1 1 0 unused

1 1 1 unused

10:1 -

Reserved (read back 0)

0 BROMEN

Boot ROM Enable: This is used by the PCI BIOS to enable accesses to Boot ROM.

ILR: Interrupt Line Register

The Interrupt Line Register is an 8-bit register used to communicate with the routing of the interrupt. It is written by the

POST software to set interrupt line for the RTL8169.

IPR: Interrupt Pin Register

The Interrupt Pin register is an 8-bit register indicating the interrupt pin used by the RTL8169. The RTL8169 uses INTA

interrupt pin. Read only. IPR = 01h.

MNGNT: Minimum Grant Timer: Read only

Specifies how long a burst period the RTL8169 needs at 33MHz clock rate in units of 1/4 microsecond. This field will be

set to a value from the external EEPROM. If there is no EEPROM, this field will default to a value of 20h.

MXLAT: Maximum Latency Timer: Read only

Specifies how often the RTL8169 needs to gain access to the PCI bus in unit of 1/4 microsecond. This field will be set to

a value from the external EEPROM. If there is no EEPROM, this field will default to a value of 20h.

Loading...

Loading...