RL78/G11 UART Reception in STOP Mode Using Middle-speed On-chip Oscillator IAR

R01AN3634EJ0100 Rev.1.00 Page 74 of 85

Feb. 15, 2017

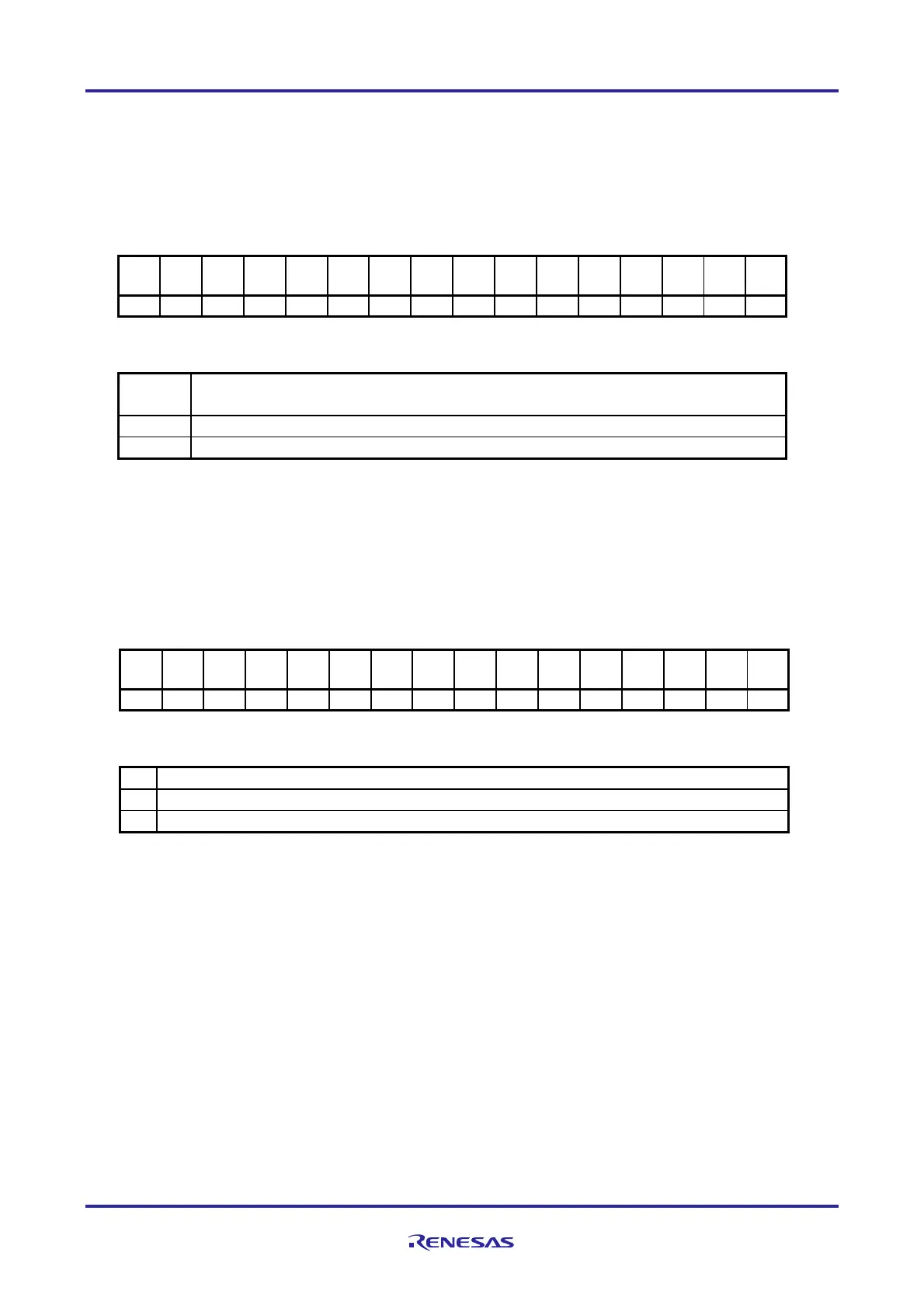

・Timer output enable register 0 (TOE0)

Set to timer output enabled.

TAU0 Channel 1 Timer Output Enable

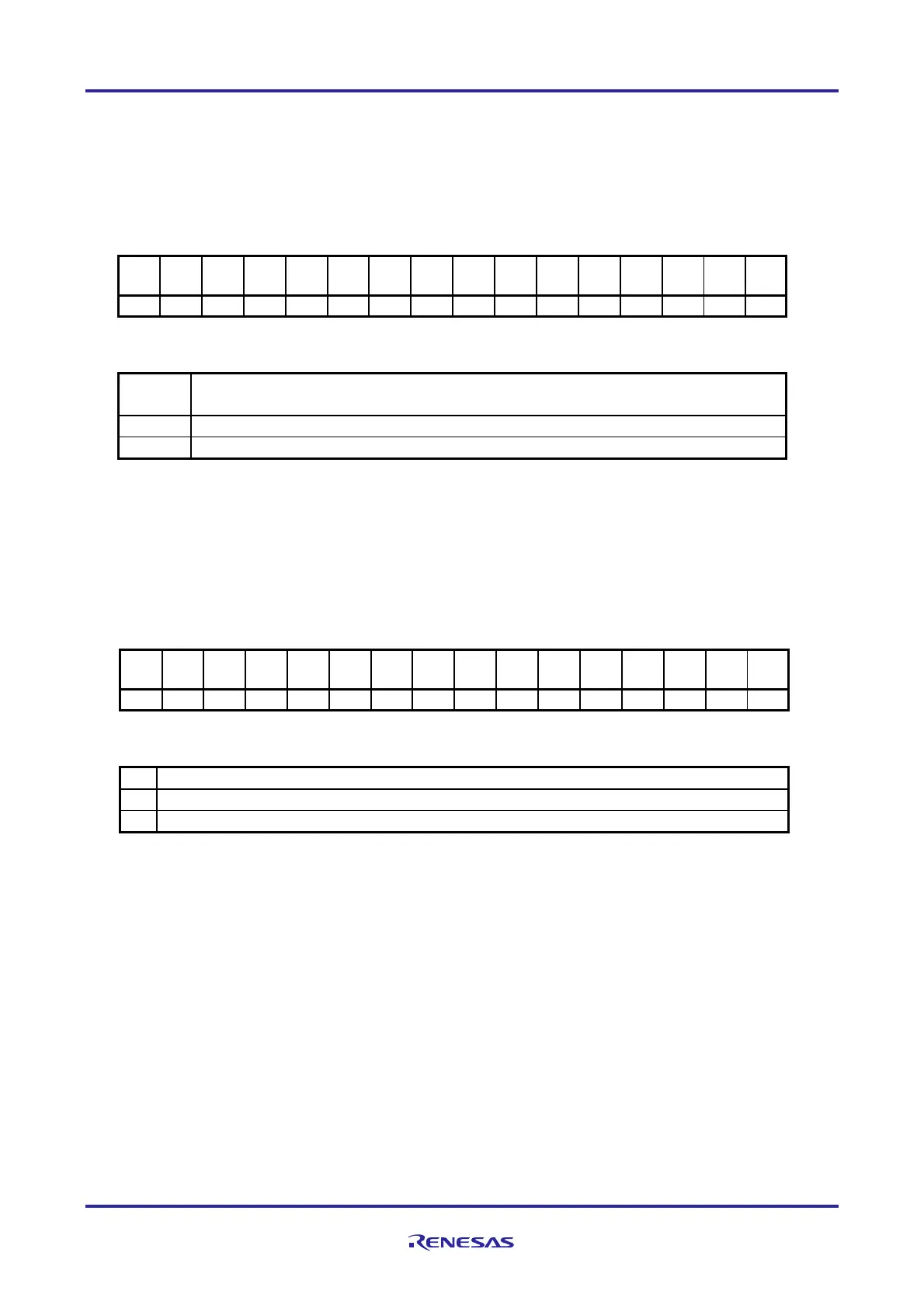

・Timer channel start register 0 (TS0)

Set to count enabled state.

TAU0 Channel 1 Operation Enable

Symbol: TS0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 TSH

03

0 TSH

01

0 0 0 0 0 TS03 TS02 TS01 TS00

x x x x x x x x x x x x x x 1 x

Bit 1

TS01 Operation enable (start) trigger for channel n

0 No trigger operation

1 TEmn bit is set to 1, goes to count operation enabled state.

Symbol: TOE0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0 0 0 0 0 TOE0

3

TOE0

2

TOE0

1

TOE0

0.

x x x x x x x x x x x x x x 1 x

Bit 1

TOE0

1

Timer output enable/disable of channel n

0 Disables timer output

1 Enables timer output

Loading...

Loading...