RL78/G11 UART Reception in STOP Mode Using Middle-speed On-chip Oscillator IAR

R01AN3634EJ0100 Rev.1.00 Page 59 of 85

Feb. 15, 2017

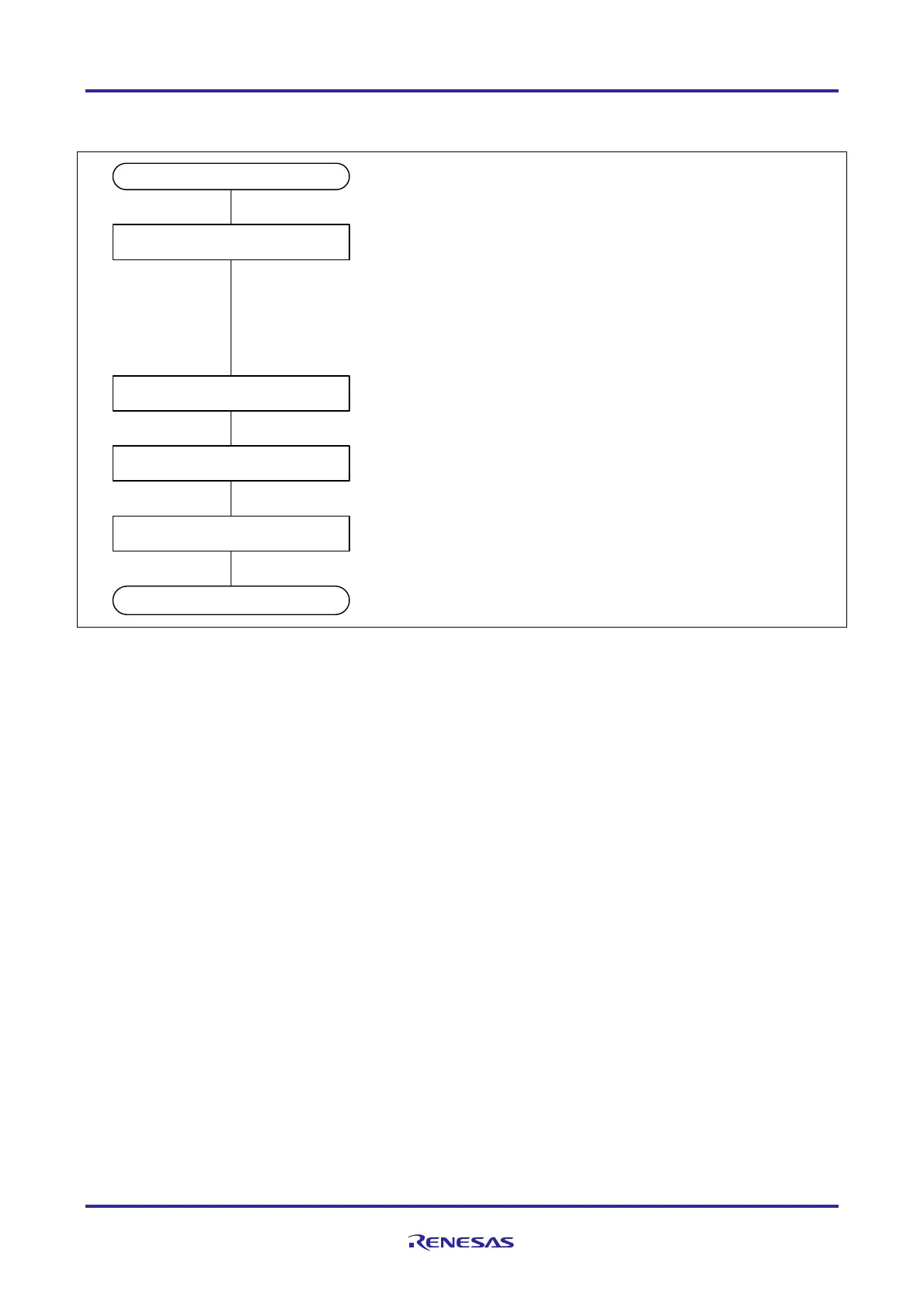

5.9.8 INTP initialization

Figure5.12 shows the INTP initialization flowchart.

R_INTC_Create

Disable all INTP interrupts

Interrupt priority level 3

(lowest priority level)

return

PR11H register

PPR111 bit ← 1

PR01H register

PPR011 bit ← 1 :Specify level 3(lowest priority level)

MK0L register

PMK5 – PMK0 bit ← 111111B :Interrupt processing disabled

MK1H register

PMK11 – PMK9 bit ← 111B :Interrupt processing disabled

MK2H register

FOMK bit ← 1 :Interrupt processing disabled

IF0L register

PIF5 – PIF0 bit ← 000000B :Interrupt request signal not generated

IF0H register

PIF11 – PIF9 bit ← 000B :Interrupt request signal not generated

IF2H register

FOIF bit ← 0 :Interrupt request signal not generated

Set external interrupt to falling edge

EGN1 register

EGN11 bit ← 1

EGP1 register

EGP11 bit ← 0 :Falling edge

Set PM55 to input mode

PM5 register

PM55 bit ← 1 :Input mode(output buffer OFF)

Figure 5.12 INTP Initialization

Loading...

Loading...