RZ Family / RZ/G, RZ/A Series 2. Functional Specifications

R01UH0990EJ0101 Rev.1.01 Page 53 of 83

Jul 28, 2022

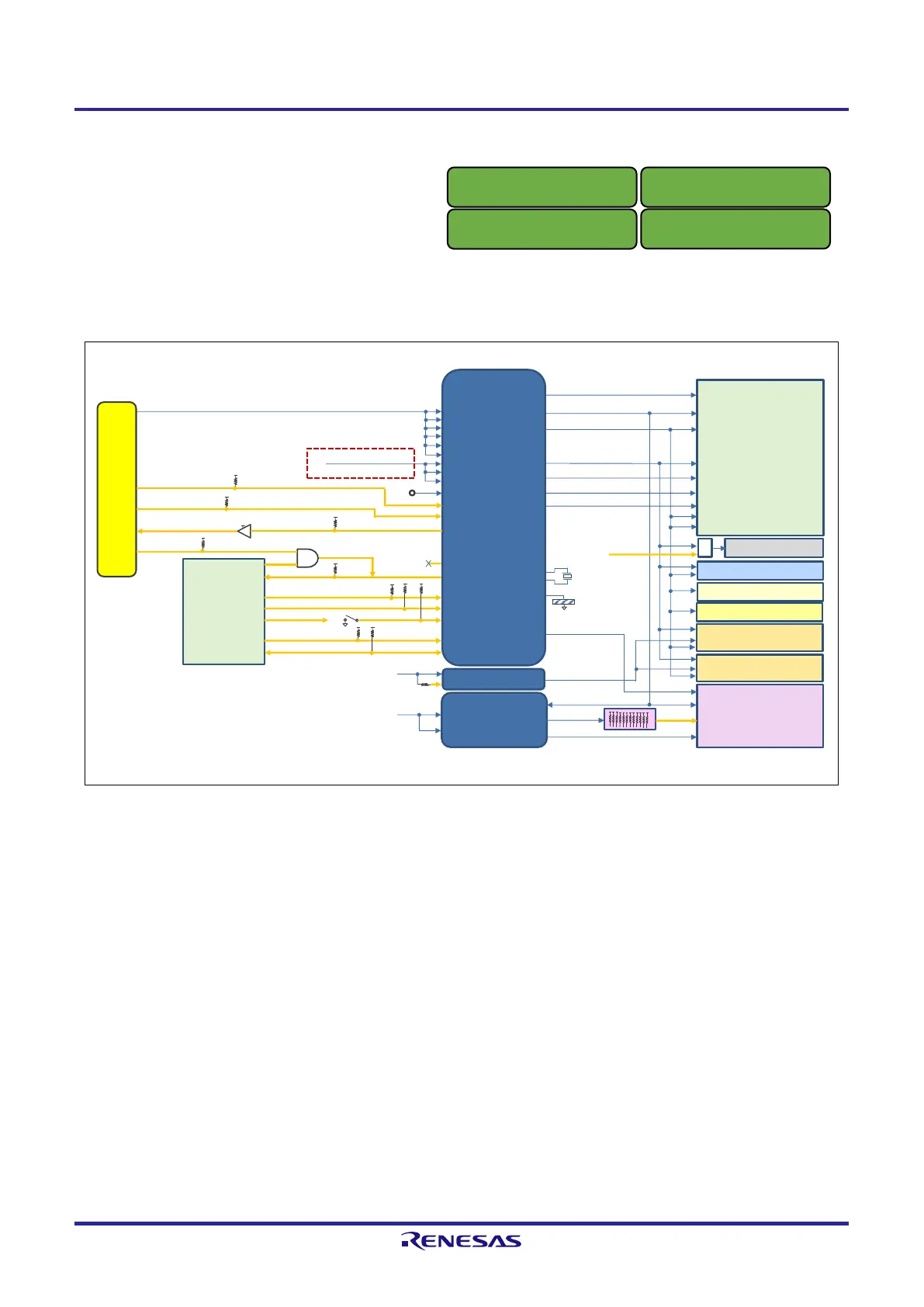

2.9 PMIC

Figure 2.11 shows the RZ/G2UL pin assignment for PMIC.

LDO2 and LDO3 output voltage value for supply SD0_PVDD and SD1_PVDD are fixed by P6_1 and P6_2.

Figure 2.11 Block Diagram around PMIC

VDD, PLLx_VDD11

SD0_PVDD

SD1_PVDD

DDR_VDDQ

VDD, PLLx_AVDD18,

CSI_VDD18(*1), USB_VDD18,

ADC_AVDD18, OTP_VDD18

ET0/1_CORE_VDD

(1.2V 1.0A)

1.1V(1.1V 2.5A)

PRST_N

PGOOD

SPI_PVDD

VTTR_DDR

(0.6V 1.5A)

DVDDH

DVDDL,AVDDL

AVDDH

DVDDH

DVDDL,AVDDL

AVDDH

VDDQ_DDR(1.2V 2.5A)

1.8V(1.8V 1.5A)

SD1_PVDD(3.3V/1.8V 0.3A)

PRST_N

RZ/G2UL

RZ/A3UL

RZ/Five

PVDD, USB_VDD33

3.3V( 3.3V 2.0A)

BUCK1

nRESET

nRESETREQ

nONKEY

DA9062

BUCK3

BUCK2

BUCK4

VTT

VLDO3

5.0V

(5.0V 5.0A)

Ether PHY 0

Ether PHY 1

PVDD182533_0

QSPI(*1)/OCTA FLASH(*2)

VCC

SMAC

Conn.

GPIO4(Sequencer cont.)

eMMC

VCC

POWER_BTN#

5.0V

VIN_PWR_BAD#

5.0V

RESET_IN#

3.3V

WDTOVF_PERROUT

CARRIER_PWR_ON

1.8V

3.3V

PMIC_PGOOD

VCCQ

VRO

DDR_VPP

VREFCA

VDD, VDDQ

VREF_DDR

(0.6V 0.1A)

VPP_DDR(2.5V 0.1A)

DDR4SDRAM

GPIO1(LDO2_GPI)

GPIO0(WDKICK)

VSYS

VDD_BUCK1

VDD_ BUCK2

VDD_ BUCK3

VDD_ BUCK4

VDD_ LDO1

VDD_ LDO2

VDD_ LDO34

VDDIO

RZ/G2UL

RZ/A3UL

RZ/Five

3.3V

3.3V

EN

NCP51200

VRI

VLDO1

OD

3.3V

XTAL_IN

XTAL_OUT

VBBAT

nIRQ

TP

SCL

SDA

3.3V

3.3V

RIIC0_SCL

RIIC0_SDA

VCC

32KHz

VCC

OCTA RAM(*2)

uSD-Card

VCC

SW

SD0_PWR_SEL

Px_x0

Px_x1

3.3V

(Dropout Typ100mV)

SW_ET0_EN

Px_x2

RZ_Px_x2

EN

GPIO2(LDO3_GPI)

GPIO3(LDO4_GPI)

SD1_PWR_SEL

3.3V

3.3V

SD0_PVDD(3.3V/1.8V 0.3A)

VLDO2

VLDO4

PVDD182533_1

SD0_PWR_

ISL80510

EN

3.3V

ET0_PVDD(3.3V/1.8V 0.3A)

(*1) RZ/A3UL SMARC Module Board OCTAL Edition is not supported.

(*2) RZ/G2UL SMARC Module Board, RZ/Five SMARC Module Board

and RZ/A3UL SMARC Module Board QSPI Edition are not supported.

RZ/A3UL SMARC Module Board

OCTAL Edition

RZ/A3UL SMARC Module Board

QSPI Edition

RZ/G2UL SMARC Module Board

RZ/Five SMARC Module Board

Loading...

Loading...