2008-03-14

LC-32A28L, LC-42A48L

55

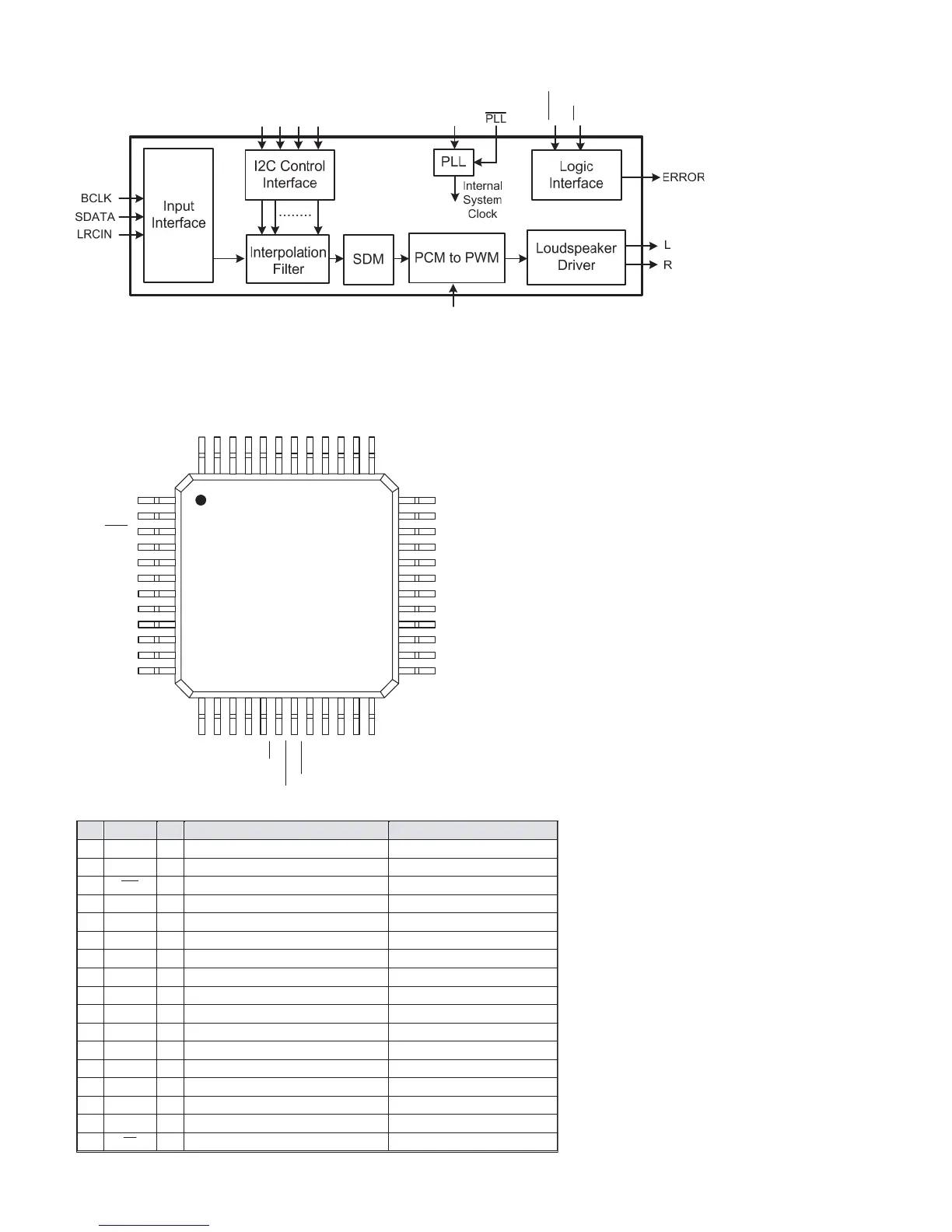

2.4. U602 (AD82581B-LEG LQFP-48 12W)

2.4.1 Block Diagram

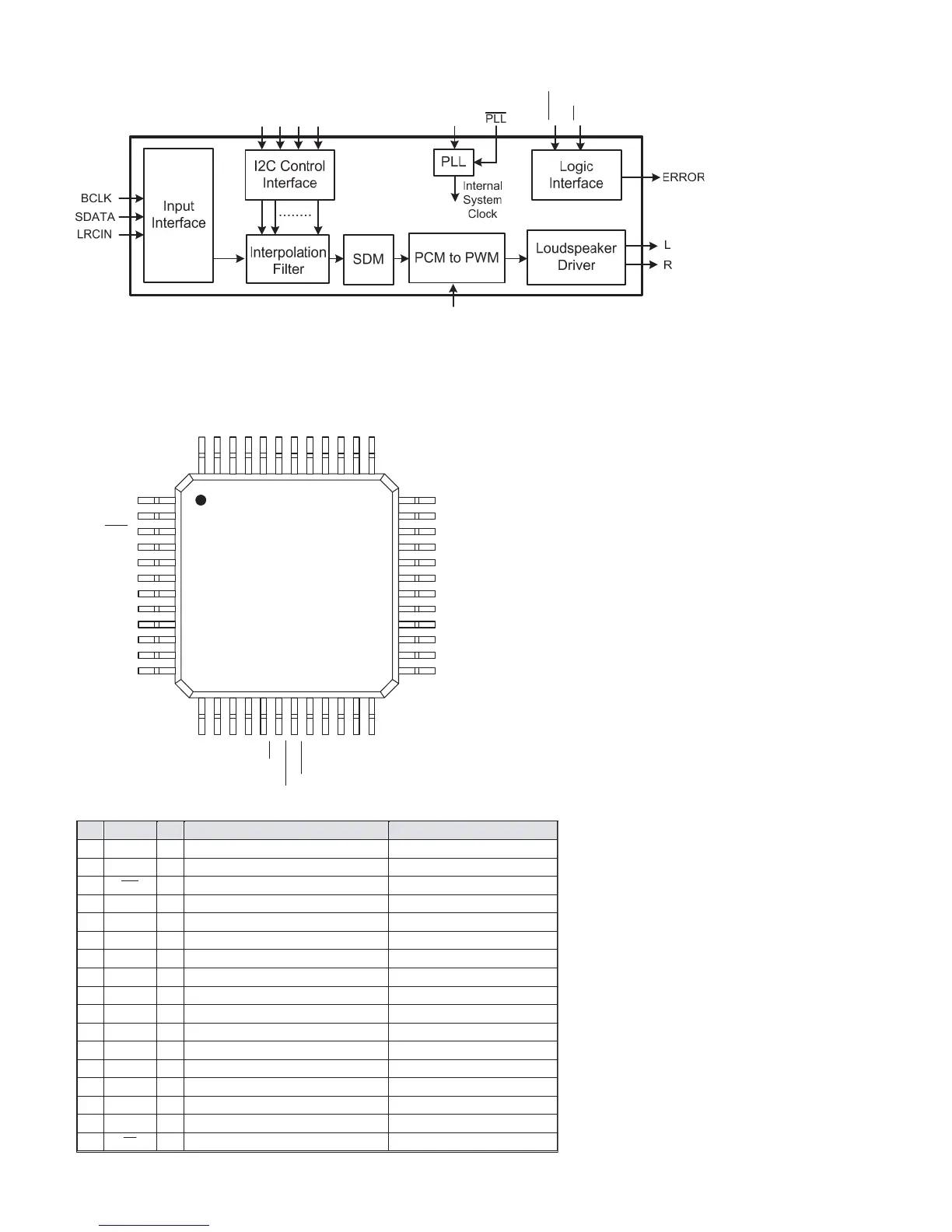

2.4.2 Pin Connections and short description

Pin Descriptions

$6

$6

$

'

6

/&6

21

2

0

WHVH5

'3

./&0

0&/.

&/.B287

'9''

'*1'

'()

6'$7$

2

1

20

1,

&

5

/

1&

1&

6'$

/

&

6

$6

$6

52

5

5(

'

3

$5''9

$

5

5'1*

%

5

%

/

%5'

'

9

%/''9

$/'

'

9

$

/

/'1*

3//

./

&

%

W

H

VH

5

1&

1&

'9''

'*1'

1&

&1

&1

&1

&

1

&

1

1&

1&

1&

1&

1&

1&

1&

1&

1&

PIN NAME

TYPE

DESCRIPTION CHARACTERISTICS

1 N.C.

2 N.C.

3

PLL

I PLL enable, low active Schmitt trigger TTL input buffer

4 MCLK I Master clock input Schmitt trigger TTL input buffer

5 CLK_OUT O Clock output from PLL TTL output buffer

6 DGND P Digital Ground

7 N.C.

8 DVDD P Digital Power

9 DEF I Default volume setting Schmitt trigger TTL input buffer

10 N.C.

11 N.C.

12 SDATA I Serial audio data input Schmitt trigger TTL input buffer

13 N.C

14 MONO I MONO mode enable, high active Schmitt trigger TTL input buffer

15 LRCIN I Left/Right clock input (Fs) Schmitt trigger TTL input buffer

16 BCLK I Bit clock input (64Fs) Schmitt trigger TTL input buffer

17

PD

I Power down, low active Schmitt trigger TTL input buffer

Loading...

Loading...