HCD-EP50

2828

3.1 Vp-

13.5 µs

7 Vp-

13.5 µs

2.4 Vp-

139 ns

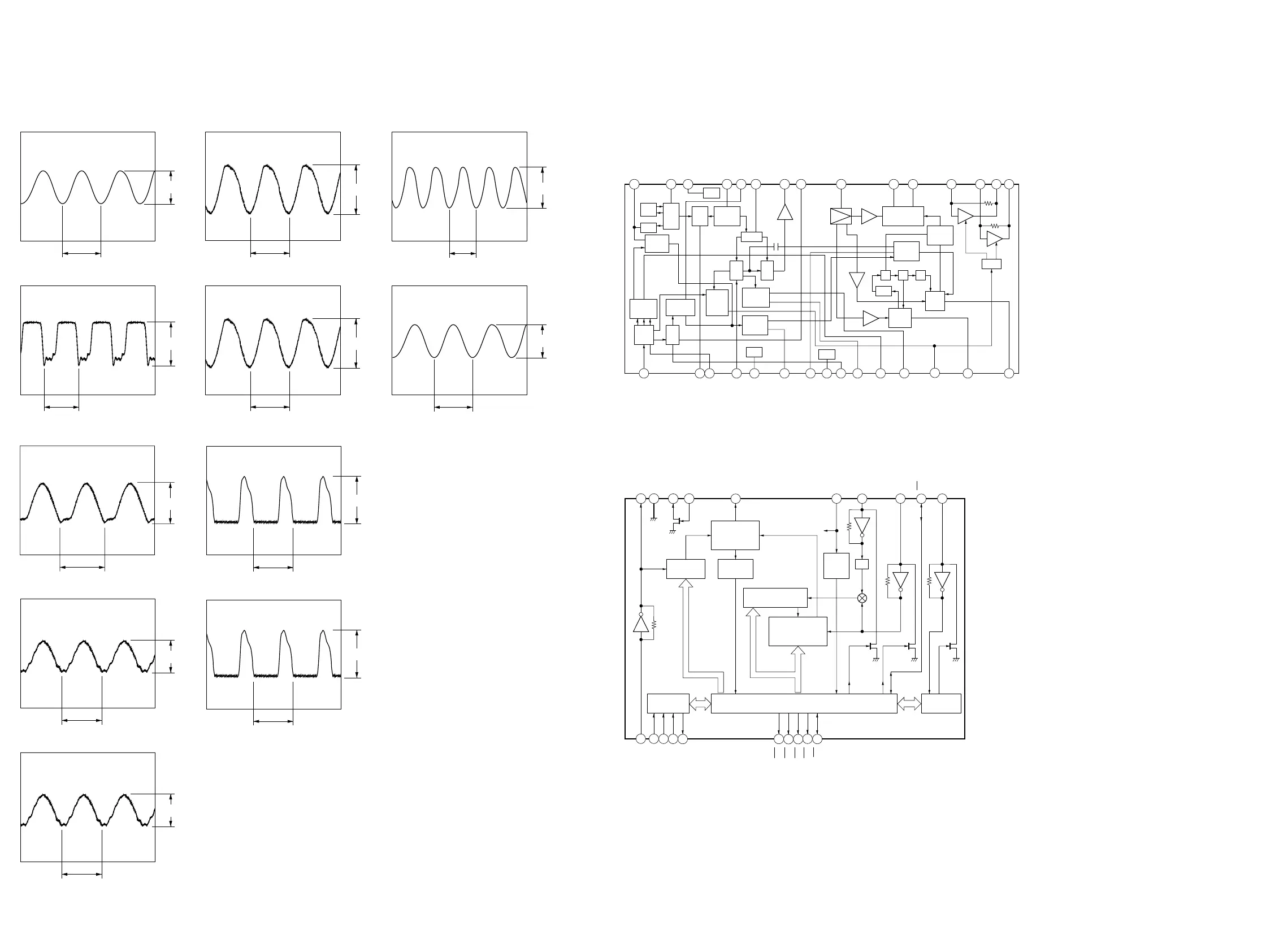

• Waveforms

– MAIN Board –

1 U2 w; (X2) 4 Q31 (Base) (REC (ISS 1) mode)

2 Q41 (Collector) (REC (ISS 1) mode)

5.1 Vp-

238 ns

– DISPLAY Board –

1 IC301 7 (X2)

110 Vp-

12.5 µs

2 Q41 (Collector) (REC (ISS 2) mode)

10 Vp-

13.5 µs

3 Q31 (Collector) (REC (ISS 1) mode)

3.1 Vp-

231 ns

2 IC305 qd (XI)

3.1 Vp-

12.5 µs

4 Q31 (Base) (REC (ISS 2) mode)

620 mVp-p

13.5 µs

5 Q31 (Emitter) (REC (ISS 1) mode)

620 mVp-p

12.5 µs

5 Q31 (Emitter) (REC (ISS 2) mode)

10 Vp-

12.5 µs

3 Q31 (Collector) (REC (ISS 2) mode)

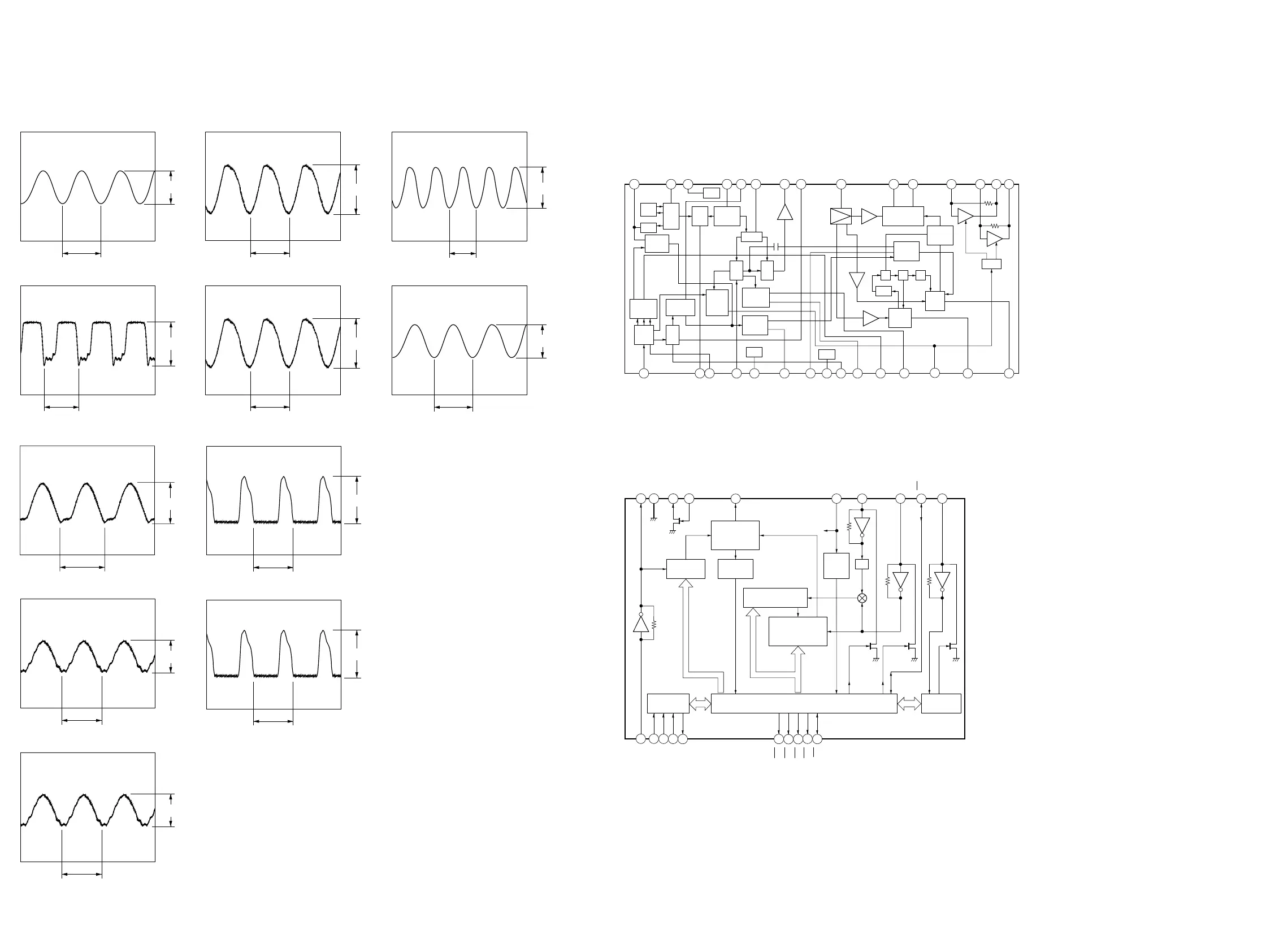

• IC Block Diagrams

– MAIN Board –

U1 LA1837L

U2 LC72131M-TL-M

ALC

BUFF

AM

OSC

AM

MIX

AM

RF. AMP

AGC

IF

DET

S-CURVE

AM/FM

IF-

BUFF

REG

TUNING

DRIVE

GND

VCC

PILOT

DET

VCO

FF

STEREO

DRIVE

STEREO

SW

MUTE

FF FF

FM

IF

FM

DET

DECODER

ANT 1-BIRDIE

1

2 3 4 5 6 7 98

20 19 18 17 16

15141110

212223242527 262930

OSC.BUFF

FM-SD.ADJ

AM-OSC

REG

FM-AFC

AM-RF-IN

AGC

MPX-IN

FM-DET OUT

AM-DET OUT

OUT L

OUT R

AMP-IN L

AMP-IN R

AMP OUT R

AMP OUT L

VCO-STOP

STEREO

AM/FM

AM. SD

FM. SD

AM. SD ADJ

IF-BUFF

MUTE

VCC

FM DET

FM-IN

AM-MIX

FM-IF

AM-IF

GND

TUNED

S-METER

FM

S-METER

AM

COMP

SD

AM

12

13

PHASE

DET

28

PHASE

DETECTOR

CHARGE PUMP

SWALLOW COUNTER

1/16, 1/17 4BITS

12BITS

PROGRAMMABLE

DRIVER

UNIVERSAL

COUNTER

REFERENCE

DIVIDER

POWER

ON

RESET

1/2

CCB

INTERFACE

1

2

3

4

5

6

7

8

9

16

15

14

13

12

11

10

17

18

1920

XOUT

VSS

AOUT

AIN

PD

VDD

FMIN

AMIN

XIN

DO

CL

DI

CE

IFIN

IO1

BO4

BO3

BO2

BO1

IO2

UNLOCK

DETECTOR

DATA SHIFT REGISTER LATCH

Loading...

Loading...