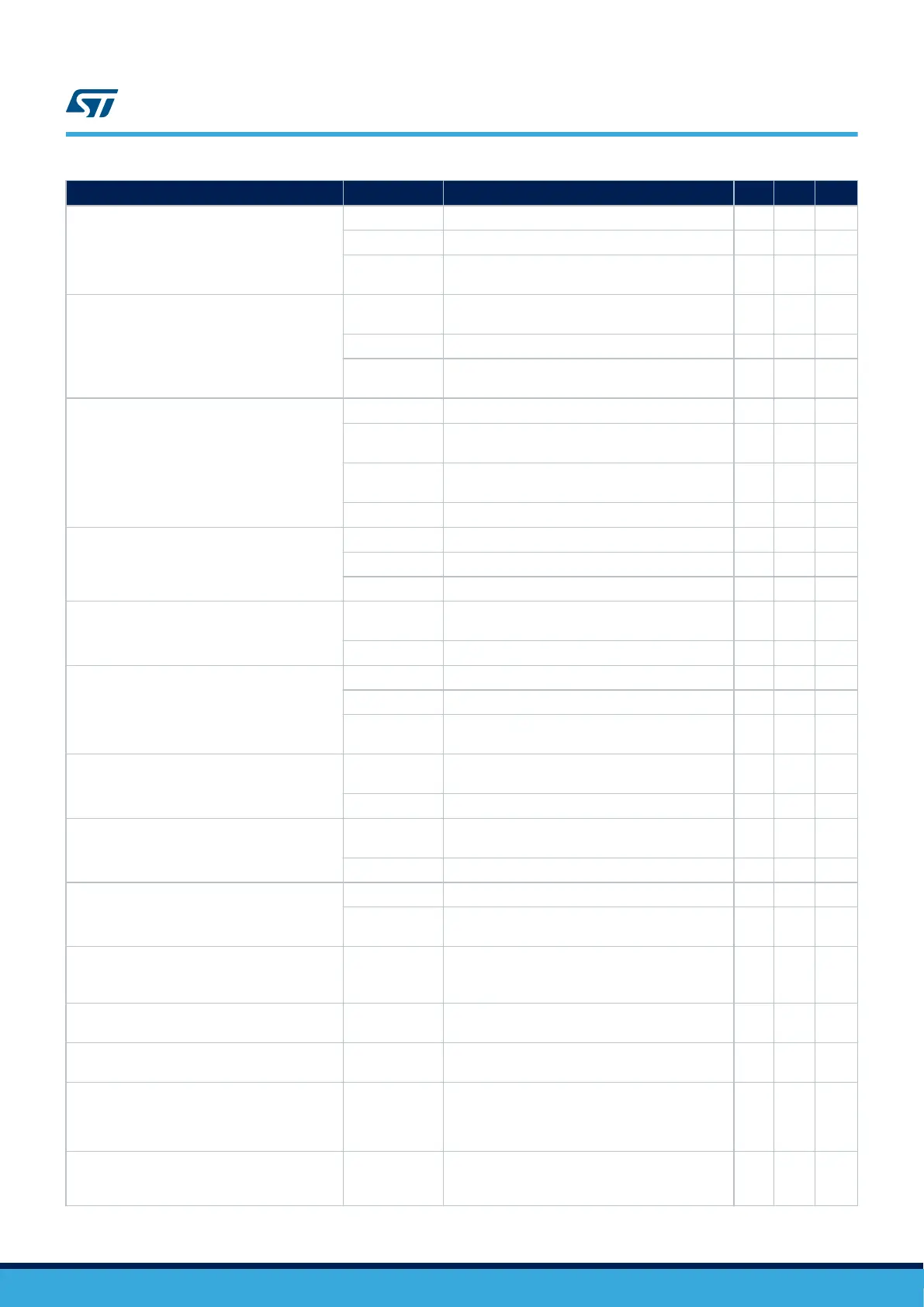

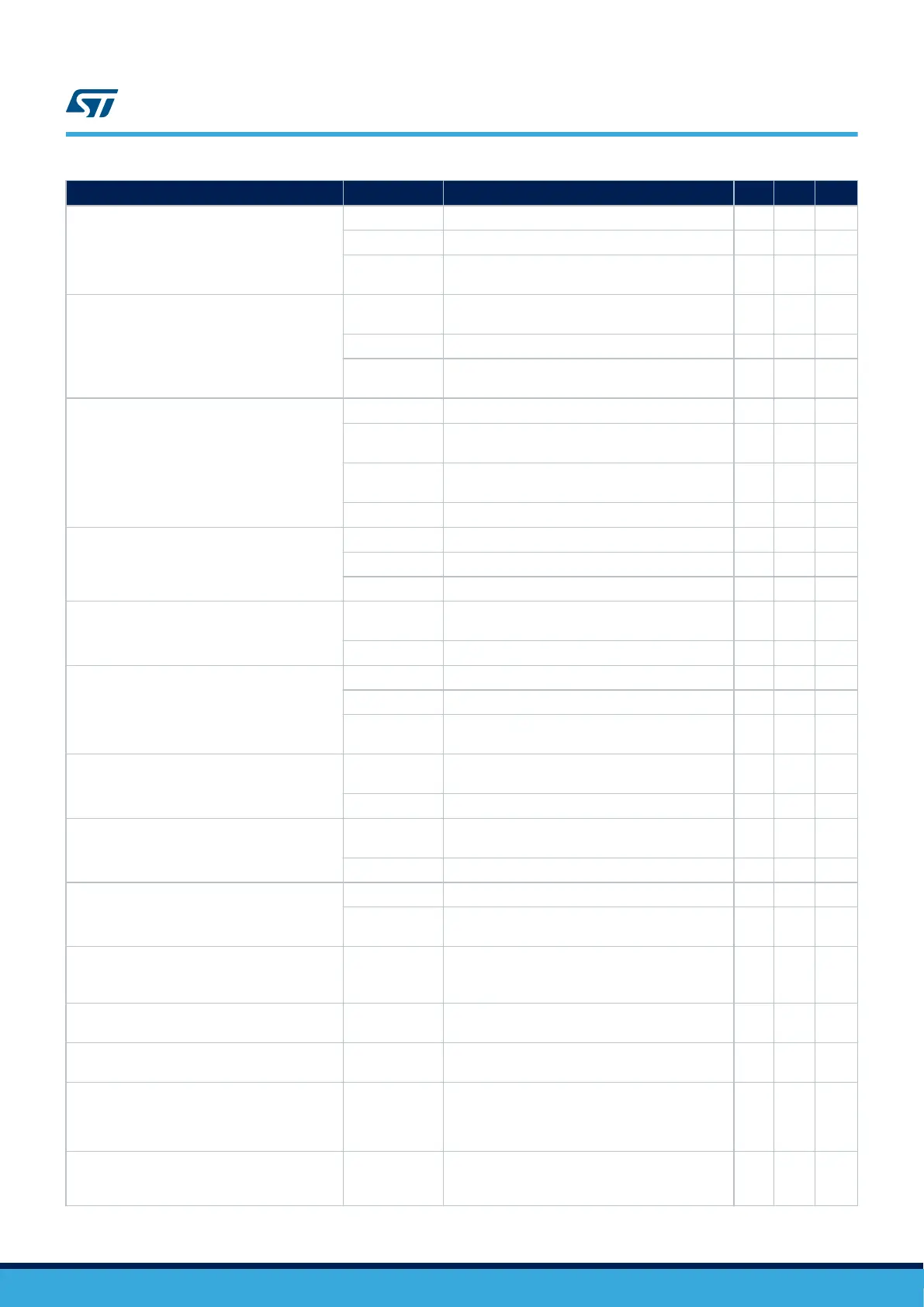

STM32F2 Series function Diagnostic Description Rank Perm Trans

System or peripheral control

LOCK_SM_0 Lock mechanism for configuration options + - -

SYSCFG_SM_0 Periodical read-back of configuration registers ++ X X

DIAG_SM_0

Periodical read-back of hardware diagnostics

configuration registers

++ X X

Ethernet (ETH): media access control (MAC)

with DMA controller

ETH_SM_0

Periodical read-back of Ethernet configuration

registers.

++ X X

ETH_SM_1 Protocol error signals including hardware CRC ++ X X

ETH_SM_2

Information redundancy techniques on messages,

including end to end safing

++ X X

Flexible static memory controller (FSMC)

FSMC_SM_0 Control flow monitoring in application software

++

(4)

X X

FSMC_SM_1

Information redundancy on external memory

connected to FSMC

++

(4)

X X

FSMC_SM_2

Periodical read-back of FSMC configuration

registers.

++ X X

FSMC_SM_3 ECC engine on NAND interface in FSMC module o X X

SAI

SAI_SM_0 Periodical read-back of SAI configuration registers ++ X X

SAI_SM_1 SAI output loopback scheme ++ X X

SAI_SM_2 1oo2 scheme for SAI module ++ X X

RNG

RNG_SM_0

Periodical read-back of RNG configuration register

RNG_CR.

++ X X

RNG_SM_1 RNG module entropy on-line tests ++ X -

AES

AES_SM_0 Periodical read-back of AES configuration registers ++ X X

AES_SM_1 Encryption/decryption collateral detection ++ X X

AES_SM_2

Information redundancy techniques on messages,

including end-to-end safing

++ X X

HASH

HASH_SM_0

Periodical read-back of HASH configuration

registers

++ X X

HASH_SM_1 HASH processing collateral detection ++ X X

DCMI

DCMI_SM_0

Periodical read-back of DCMI configuration

registers

++ X X

DCMI_SM_1 DCMI video input data synchronization ++ X -

Part separation (no interference)

FFI_SM_0 Unused peripherals disable ++ X -

FFI_SM_1

Periodical read-back of interference avoidance

registers

++ - -

Arm

®

Cortex

®

-M3 CPU

CoU_1

The reset condition of Arm

®

Cortex

®

-M3 CPU

must be compatible as valid safe state at system

level

++ - -

Debug CoU_2

STM32F2 Series debug features must not be used

in safety function(s) implementation

++ - -

Arm

®

Cortex

®

-M3 / Supply system

CoU_3

Low power mode state must not be used in safety

function(s) implementation

++ - -

STM32F2 Series peripherals CoU_4

End user must implement the required combination

of safety mechanism/CoUs for each STM32

peripherals used in safety function(s)

implementation

++ X X

Flash subsystem CoU_5

During Flash bank mass erase and reprogramming

there must not be safety functions(s) executed by

STM32F2 MCU.

++ - -

UM1845

Conditions of use

UM1845 - Rev 4

page 80/108

Loading...

Loading...