Revision history PM0059

28/29 DocID15687 Rev 5

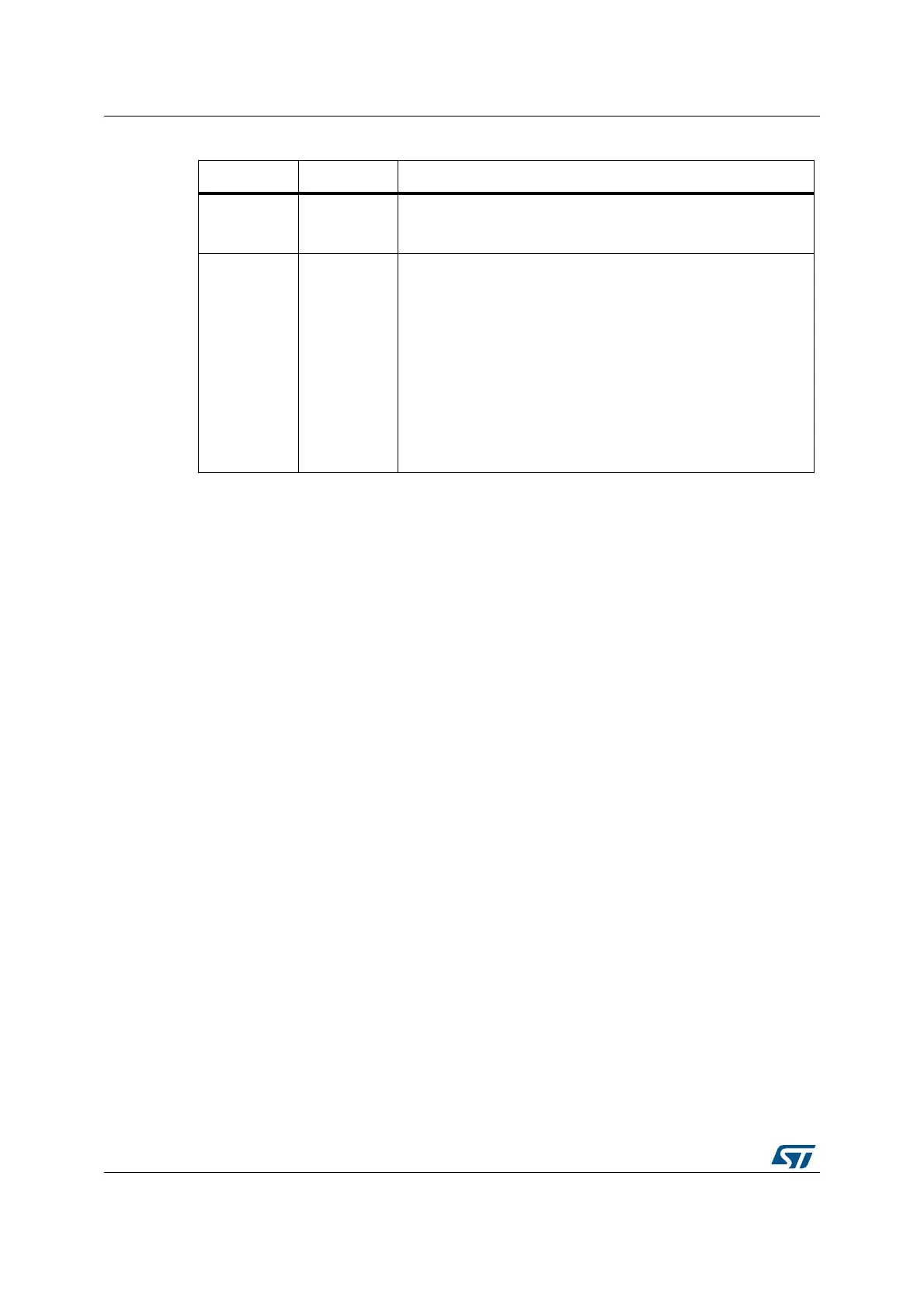

10-May-2011 4

Modified Note 1 in Table 3: Number of wait states according to

CPU clock (HCLK) frequency and Note 1 in Table 3: Number of

wait states according to CPU clock (HCLK) frequency.

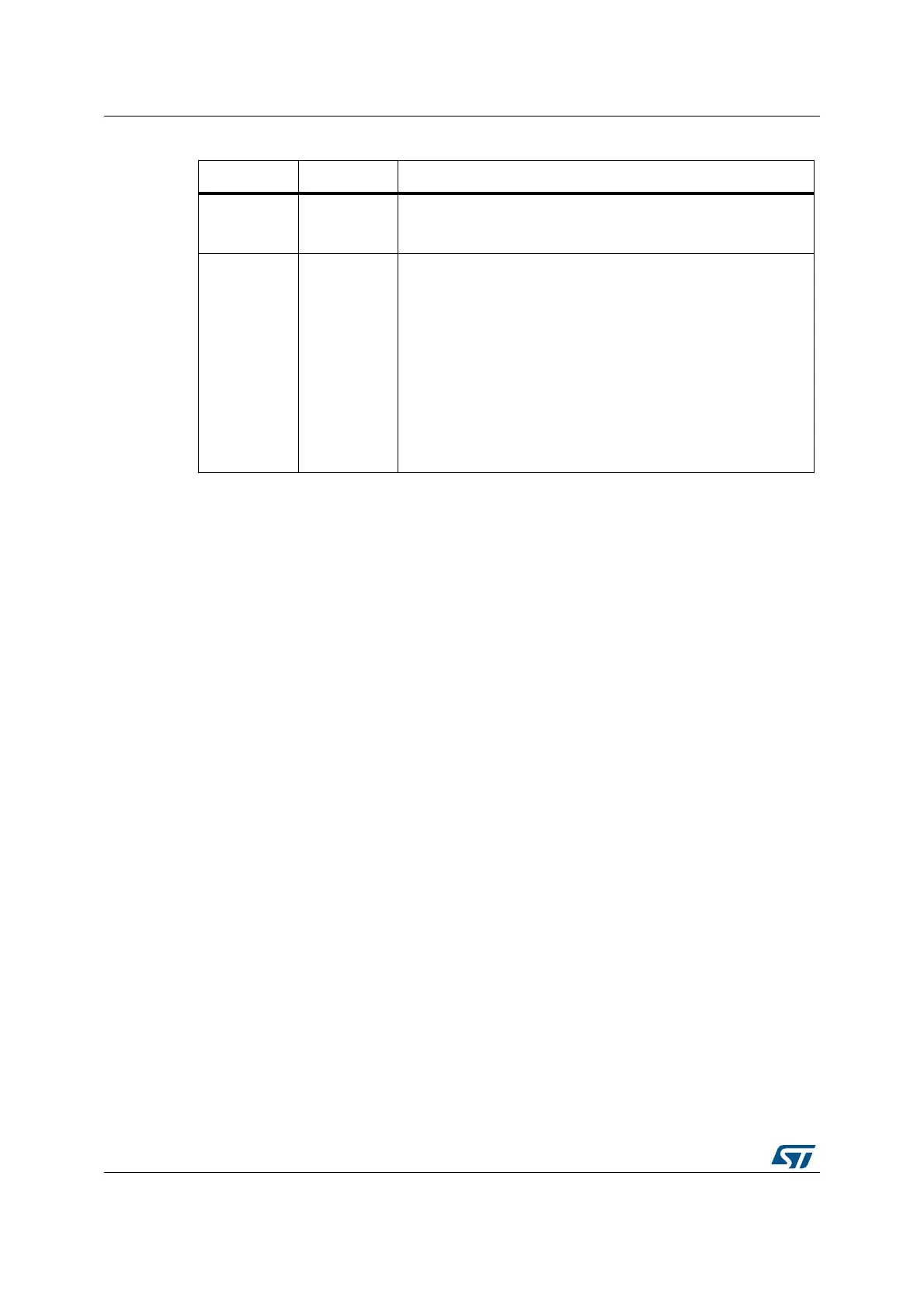

07-Jun-2013 5

Updated Section 2.4.1: Relation between CPU clock frequency

and Flash memory read time to add prefetch disabling when the

supply voltage is below 2.1 V.

Added note in Section : Standard programming

Updated Section 2.5.2: Program/erase parallelism.

Added Table 5: Flash interrupt requests.

Updated Section 2.6.3: Read protection (RDP).

Updated Section 2.6.4: Write protections.

Modified BOR_LEV bits definition in Section 2.8.6: Flash option

control register (FLASH_OPTCR).

Document converted to new template and disclaimer updated.

Table 11. Document revision history (continued)

Date Revision Changes

Loading...

Loading...