DocID027942 Rev 3 17/49

UM1907 Hardware layout and configuration

48

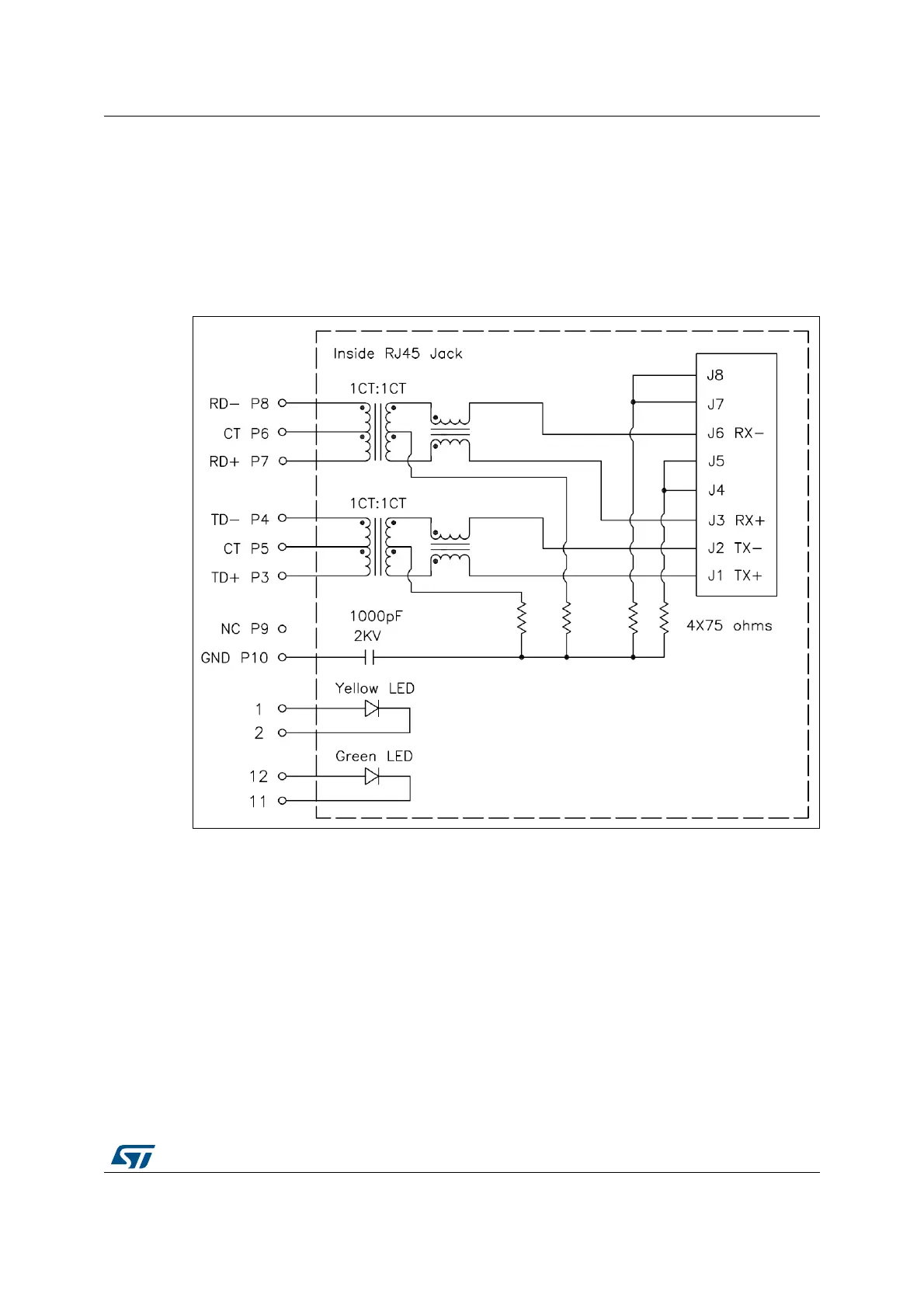

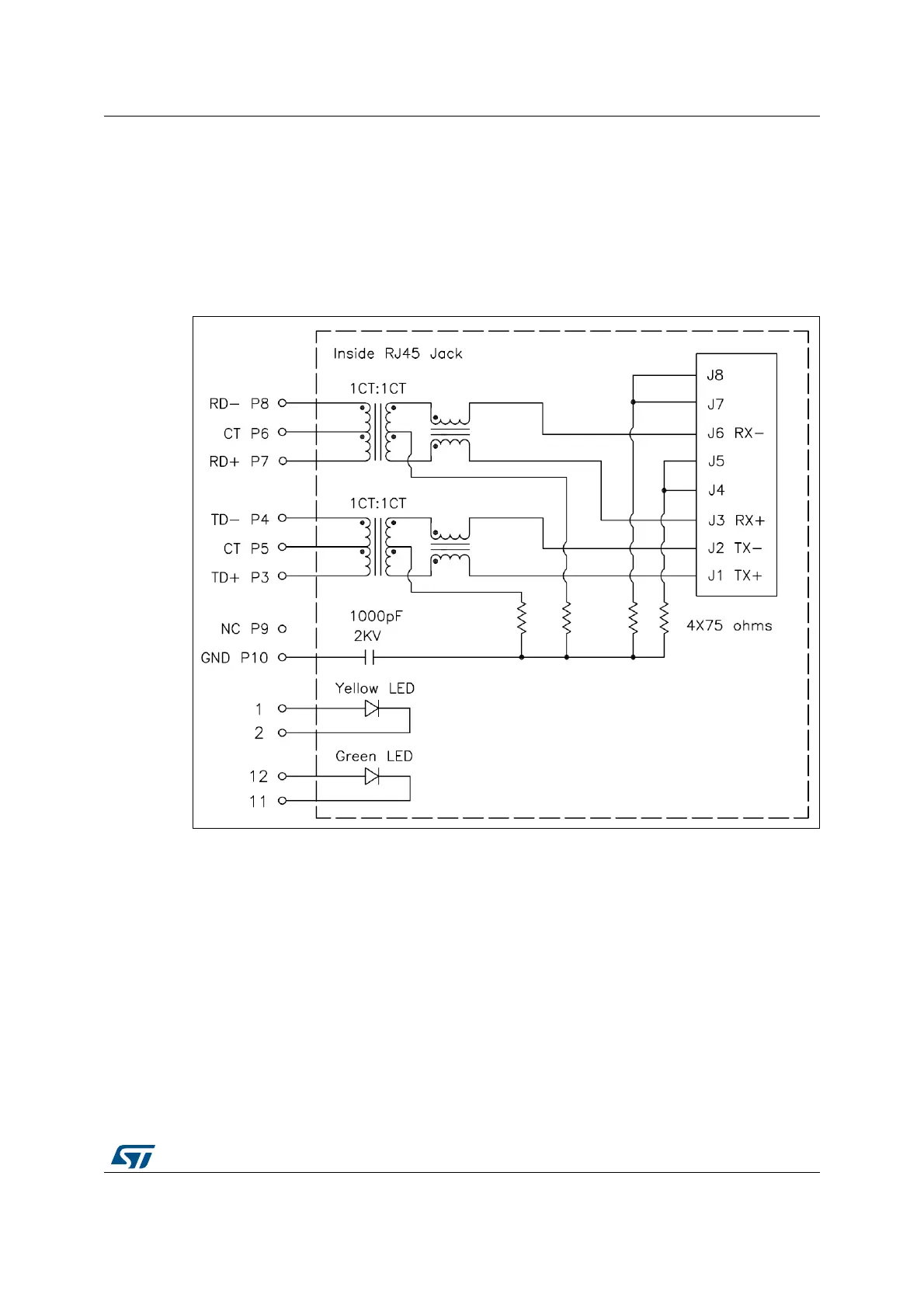

6.10 Ethernet

The STM32F746G-DISCO discovery board supports 10/100-Mbit Ethernet communication

by a PHY LAN8742A-CZ-TR (U9) from MICROCHIP and RJ45 jack (CN9). Ethernet PHY is

connected to STM32F746NGH6 via RMII interface.

25 MHz clock for the PHY is generated by the oscillator X2, the 50 MHz clock for the

STM32F746NGH6 is generated by the PHY RMII_REF_CLK.

Figure 12. Inside RJ45 jack

6.11 SDRAM memory

128-Mbit SDRAM (MT48LC4M32B2B5-6A from MICRON) is connected to the FMC

interface of the STM32F746NGH6. Only the lowest 16-bit data are used (64-Mbit

accessible). DQ16 to DQ31 are unused and connected to a 10K ohm pull-down resistor.

6.12 Quad-SPI Nor Flash memory

128-Mbit Quad-SPI Nor Flash memory (N25Q128A13EF840E from MICRON) is connected

to the Quad-SPI interface of the STM32F746NGH6.

Loading...

Loading...