PM0214 Rev 10 109/262

PM0214 The STM32 Cortex-M4 instruction set

261

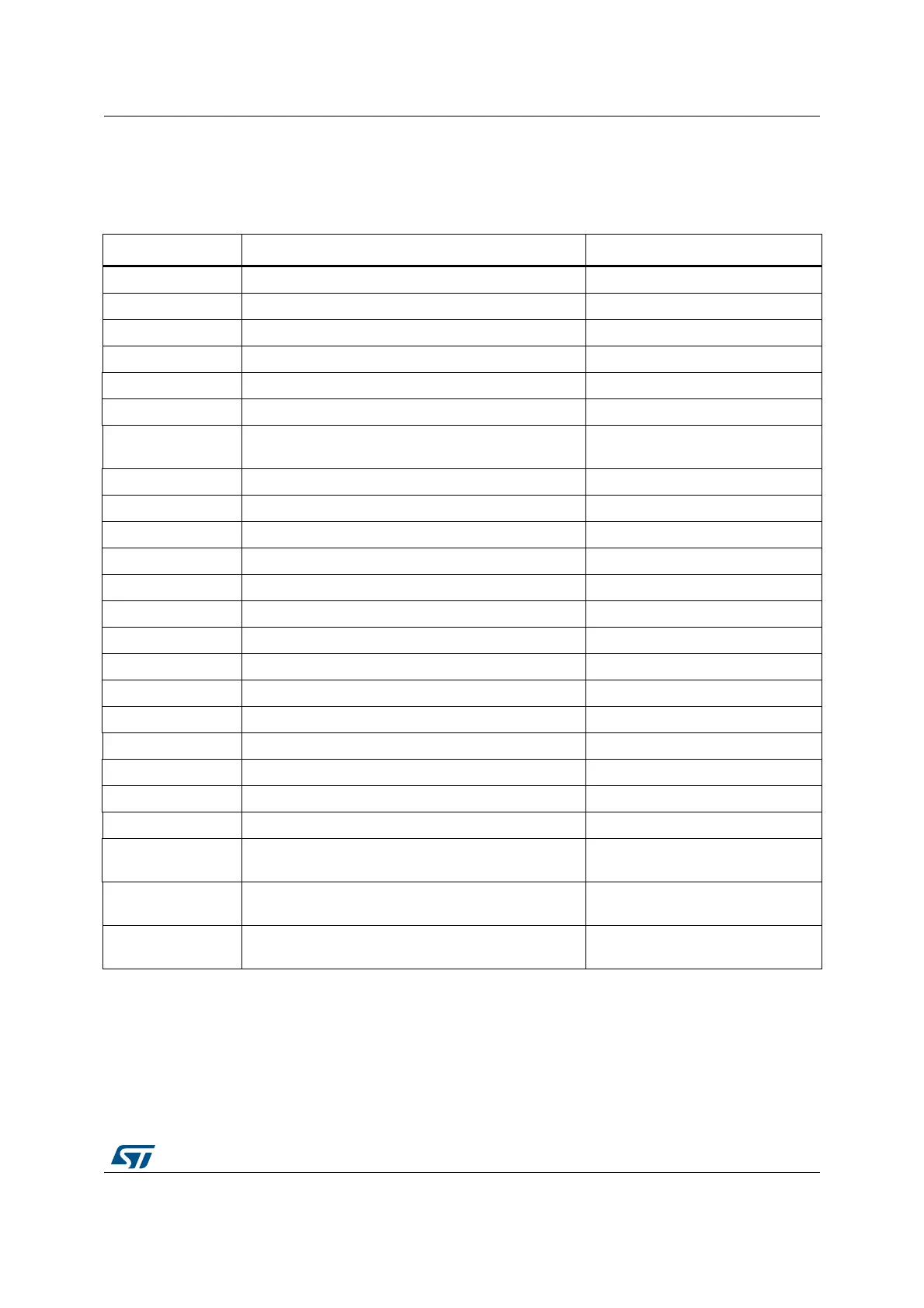

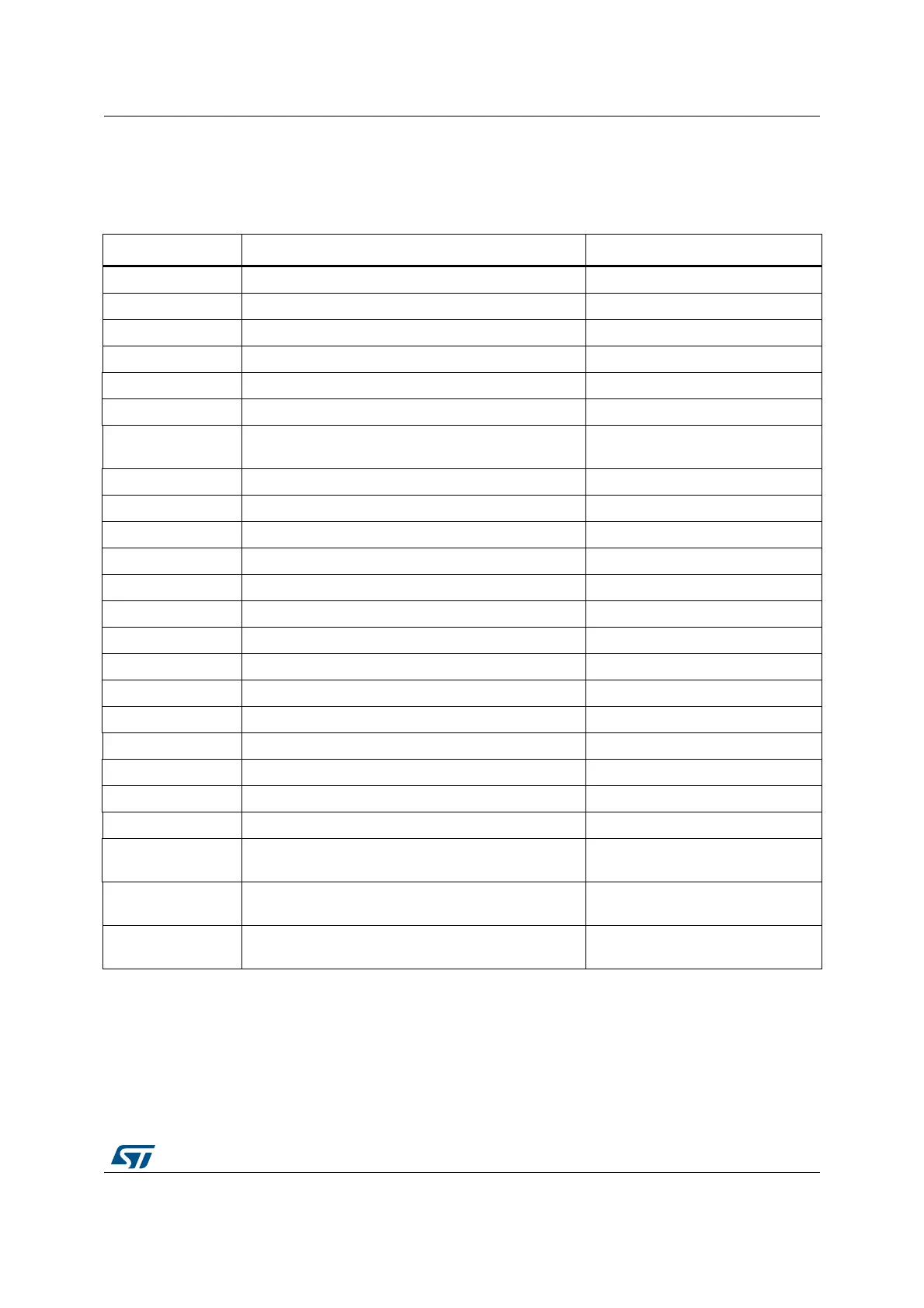

3.6 Multiply and divide instructions

Table 29 shows the multiply and divide instructions.

Table 29. Multiply and divide instructions

Mnemonic Brief description See

MLA Multiply with Accumulate, 32-bit result MUL, MLA, and MLS on page 110

MLS Multiply and Subtract, 32-bit result MUL, MLA, and MLS on page 110

MUL Multiply, 32-bit result MUL, MLA, and MLS on page 110

SDIV Signed Divide SDIV and UDIV on page 124

SMLA[B,T] Signed Multiply Accumulate (halfwords) SMLA and SMLAW on page 112

SMLAD

,

SMLADX

Signed Multiply Accumulate dual SMLAD on page 114

SMLAL

Signed Multiply with Accumulate (32x32+64), 64-bit

result

SMLAL and SMLALD on page 115

SMLAL[B,T]

Signed Multiply Accumulate Long (halfwords) SMLAL and SMLALD on page 115

SMLALD

,

SMLALDX

Signed Multiply Accumulate Long Dual SMLAL and SMLALD on page 115

SMLAW[B|T] Signed Multiply Accumulate (word by halfword) SMLA and SMLAW on page 112

SMLSD Signed Multiply Subtract Dual SMLSD and SMLSLD on page 117

SMLSLD Signed Multiply Subtract Long Dual SMLSD and SMLSLD on page 117

SMMLA Signed Most Significant Word Multiply Accumulate SMMLA and SMMLS on page 119

SMMLS

,

SMMLSR

Signed Most Significant Word Multiply Subtract SMMLA and SMMLS on page 119

SMUAD, SMUADX Signed dual multiply add SMUAD and SMUSD on page 121

SMUL[B,T] Signed multiply (word by halfword) SMUL and SMULW on page 122

SMMUL

,

SMMULR

Signed most significant word multiply SMMUL on page 120

SMULL Signed multiply (32x32), 64-bit result SMMUL on page 120

SMULWB, SMULWT Signed multiply (word by halfword) SMUL and SMULW on page 122

SMUSD, SMUSDX Signed dual multiply subtract SMUAD and SMUSD on page 121

UDIV Unsigned Divide SMLA and SMLAW on page 112

UMAAL

Unsigned Multiply Accumulate Accumulate Long

(32x32+32+32), 64-bit result

UMULL, UMAAL and UMLAL on

page 111

UMLAL

Unsigned Multiply with Accumulate (32x32+64), 64-bit

result

UMULL, UMAAL and UMLAL on

page 111

UMULL Unsigned Multiply (32x32), 64-bit result

UMULL, UMAAL and UMLAL on

page 111

Loading...

Loading...