– 23 –

THEORY OF OPERATION

2-3. Reset Circuit

The RESET signal initializes the circuit elements and prevents operation errors when the power is turned on.

The RESET signal is output for approx. 34ms. when the power is turned on, or while the RESET ( INPUT-PRIME ) signal

is being output from the host computer.

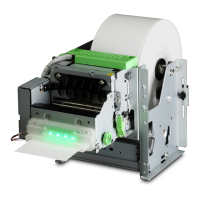

Fig. 2-13 Reset Circuit and Protection Circuit.

• Power On Reset

1 When the power is turned on, the RESET signal output from Pin 5 of IC6 (M51953BL) for approx. 34 msec. This time

length is determined by external capacitor C18 (0.1µF), and it can be calculated by the following formula.

T = 0.34 × C18 (pF) µsec.

2 This LOW signal triggers RESET command to the CPU and the RESET terminal ( RES ) of the gate array.

3 Resetting the CPU and the gate array will ignore all the drive signals for the carriage motor, the paper feed motor and

the print head, preventing operation errors at power ON.

• Reset by Input Prime Signal from Host Computer

1 The input prime signal from the host computer is output to pin 31 of the connector CN1.

2 This output signal will set the terminal INIT 2 of the CPU to LOW, executing interruption. Then, the CPU will be

initialized.

Loading...

Loading...