DWC ADC 12b5M SAR, TSMC180 IP Databook

April 2012 Synopsys, Inc. 22-30

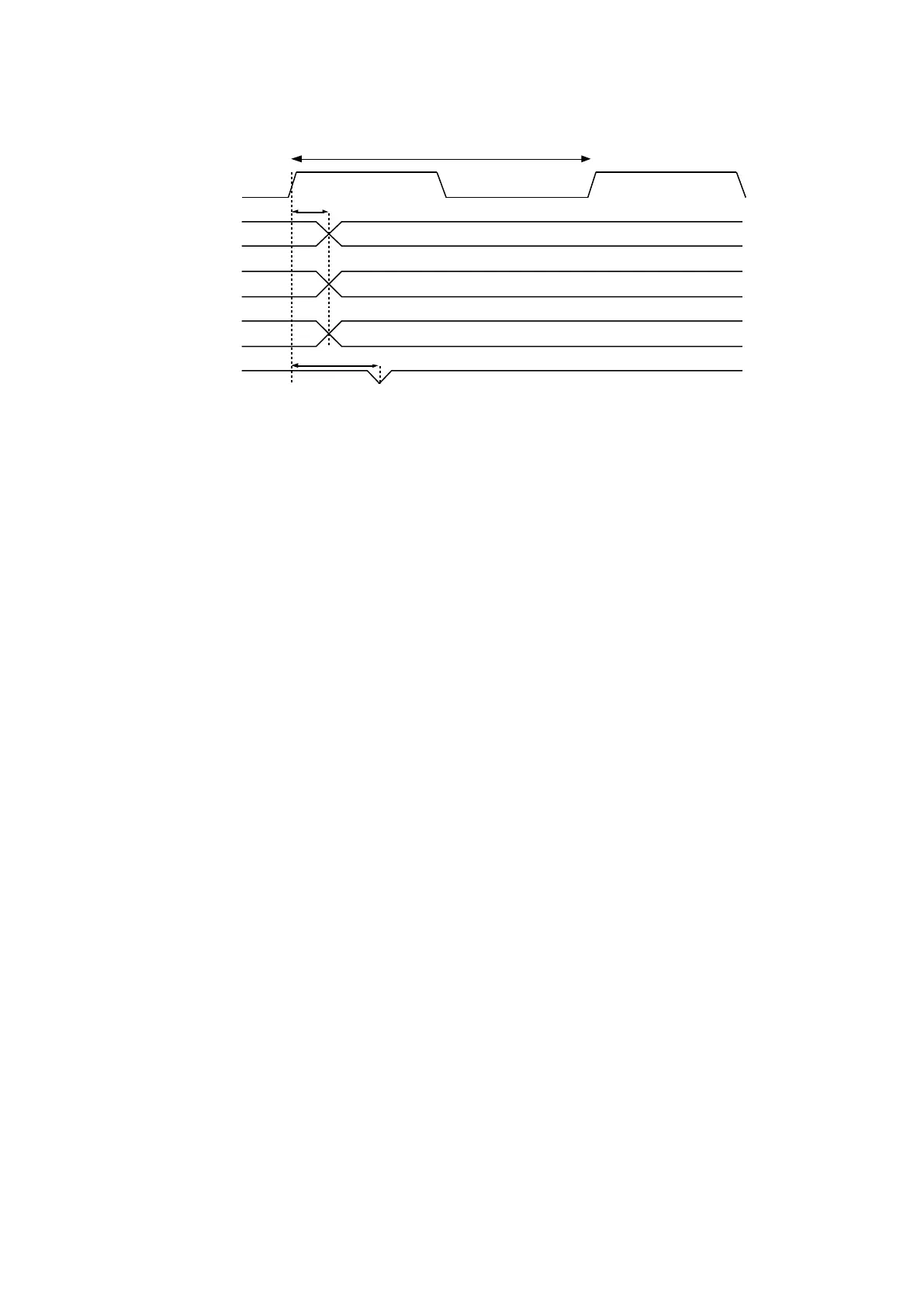

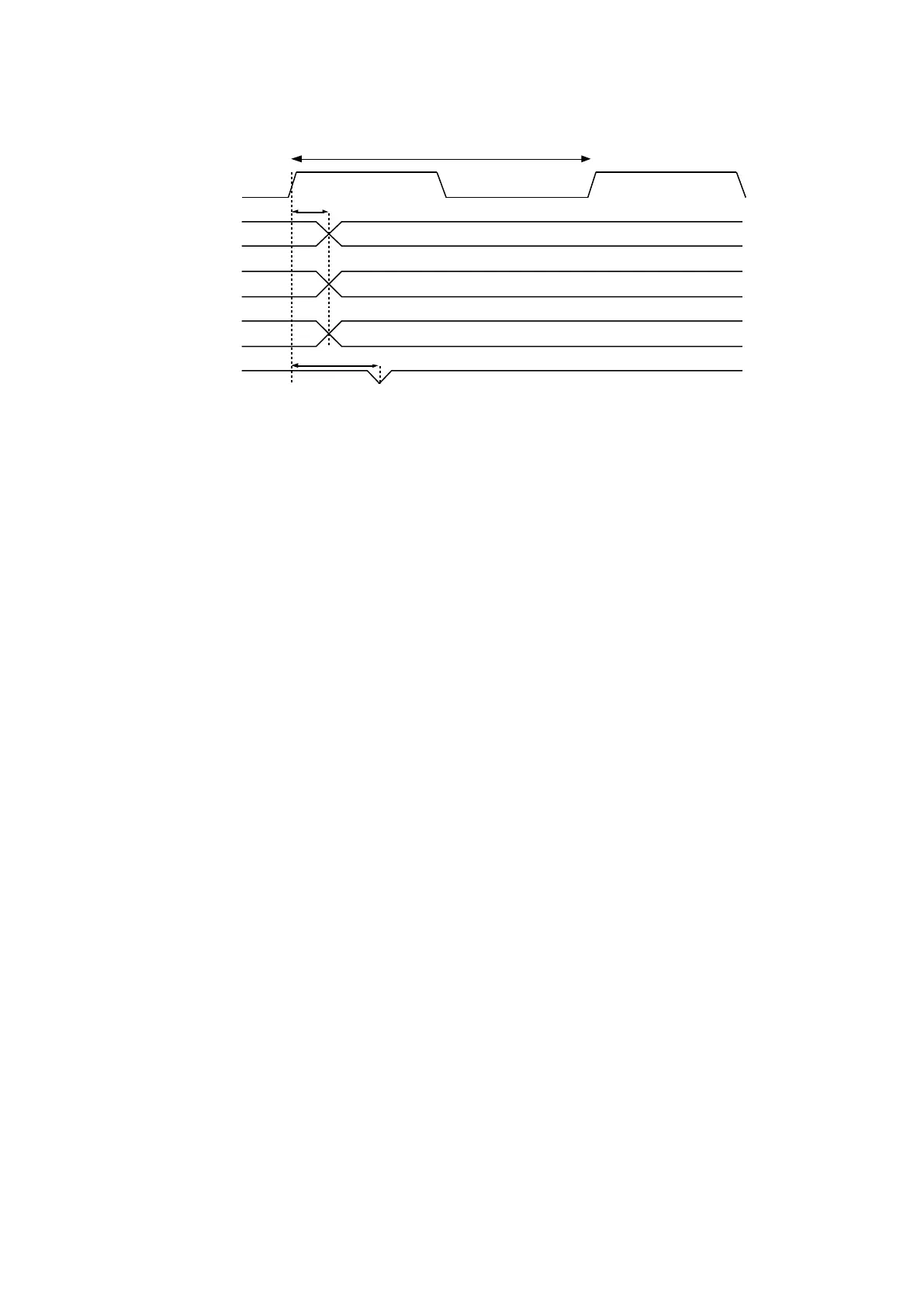

Figure 13 - Timing diagram of the scan chain signals

The scan chain coverage is 96%. All flip-flops are clocked on the rising edge of the scanclk.

The input data scanin pin should change synchronously with the rising edge of the scanclk

clock.

The output data scanout pin changes synchronously with the rising edge of the scanclk

clock.

scanclk

scanen

scanrst

scanin

scanout

tclkscan

thld

trsp

Loading...

Loading...