DWC ADC 12b5M SAR, TSMC180 IP Databook

April 2012 Synopsys, Inc. 21-30

9 Production Test

A scan chain was added to the core to enable the user to test the digital calibration block

separately if desired.

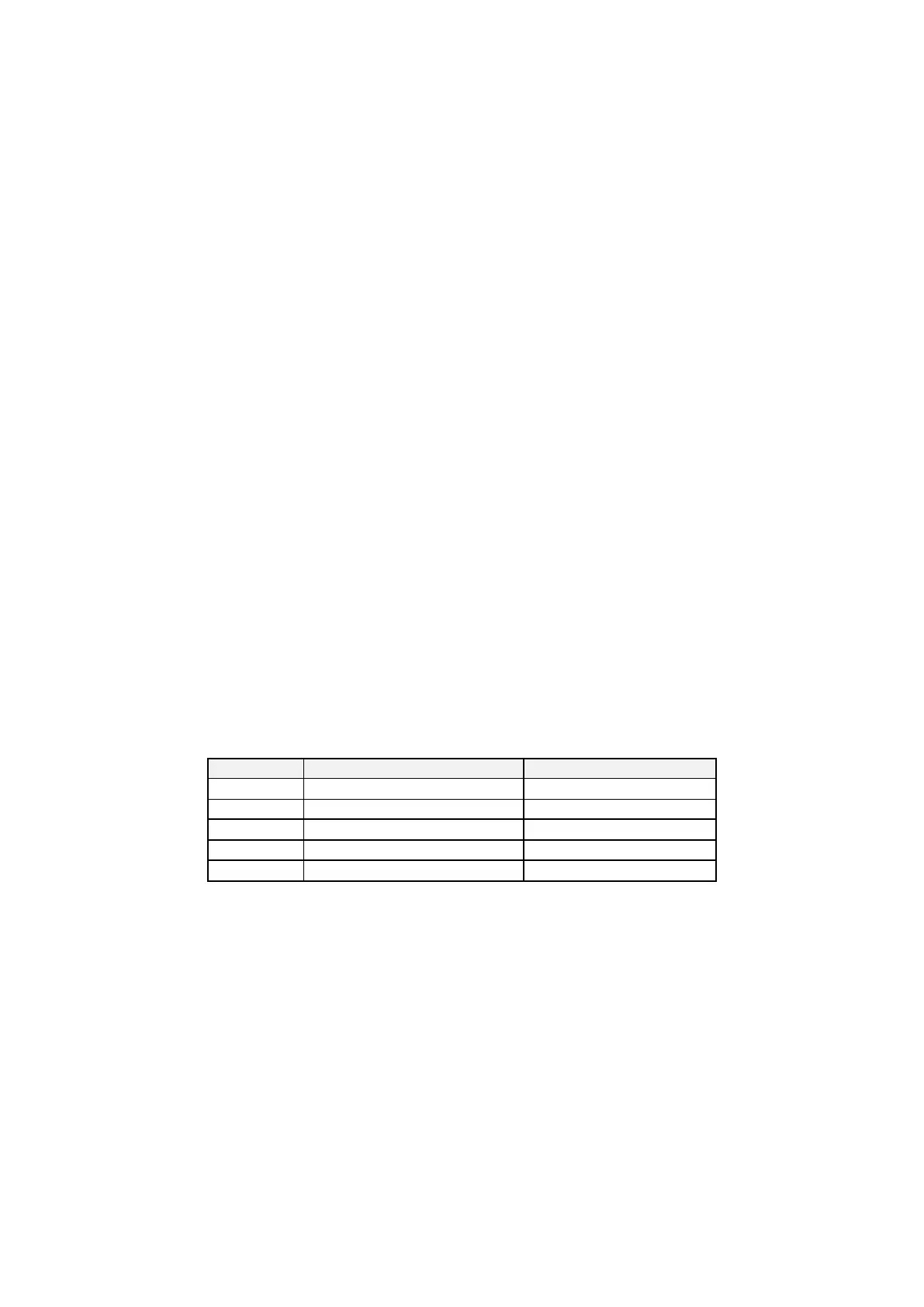

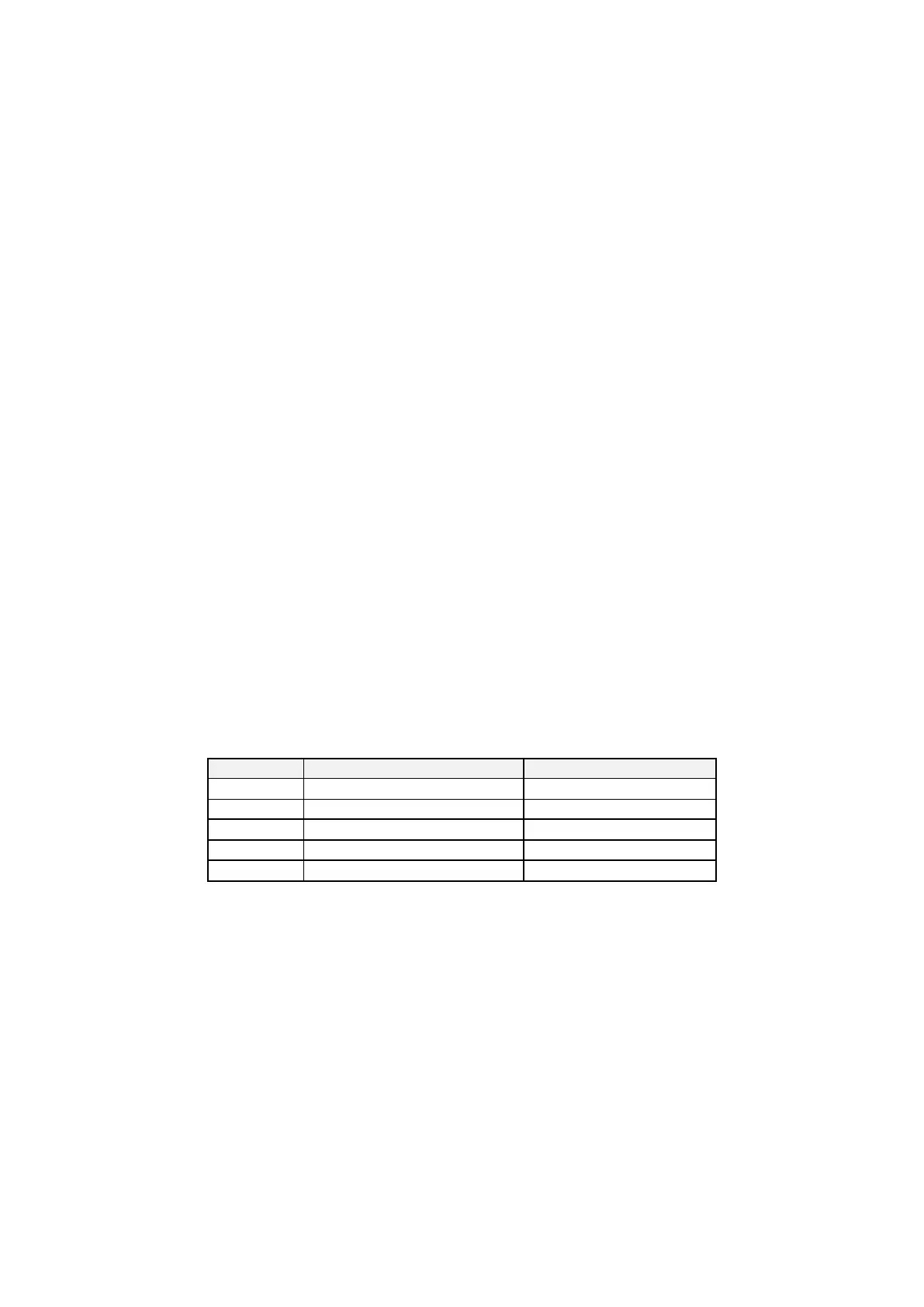

Table 3 – Scan mode pins

For scan testing the scanmode signal should be set to high in order to connect all flip-flops to

the input clock. Scan test input signal is scanin pin, test output signal is scanout pin and test

control signal is scanen. The maximum scan clock frequency is 50MHz.

Loading...

Loading...