LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

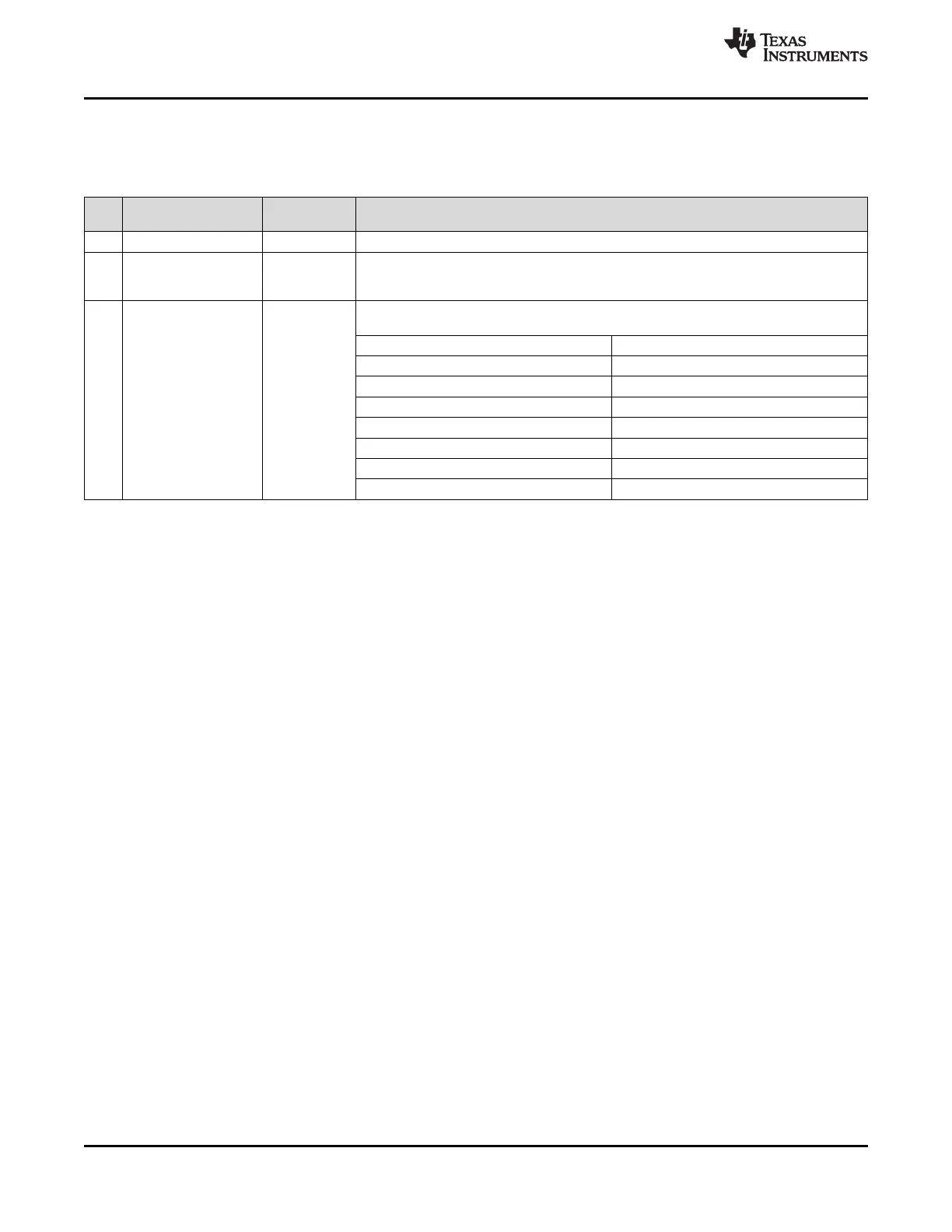

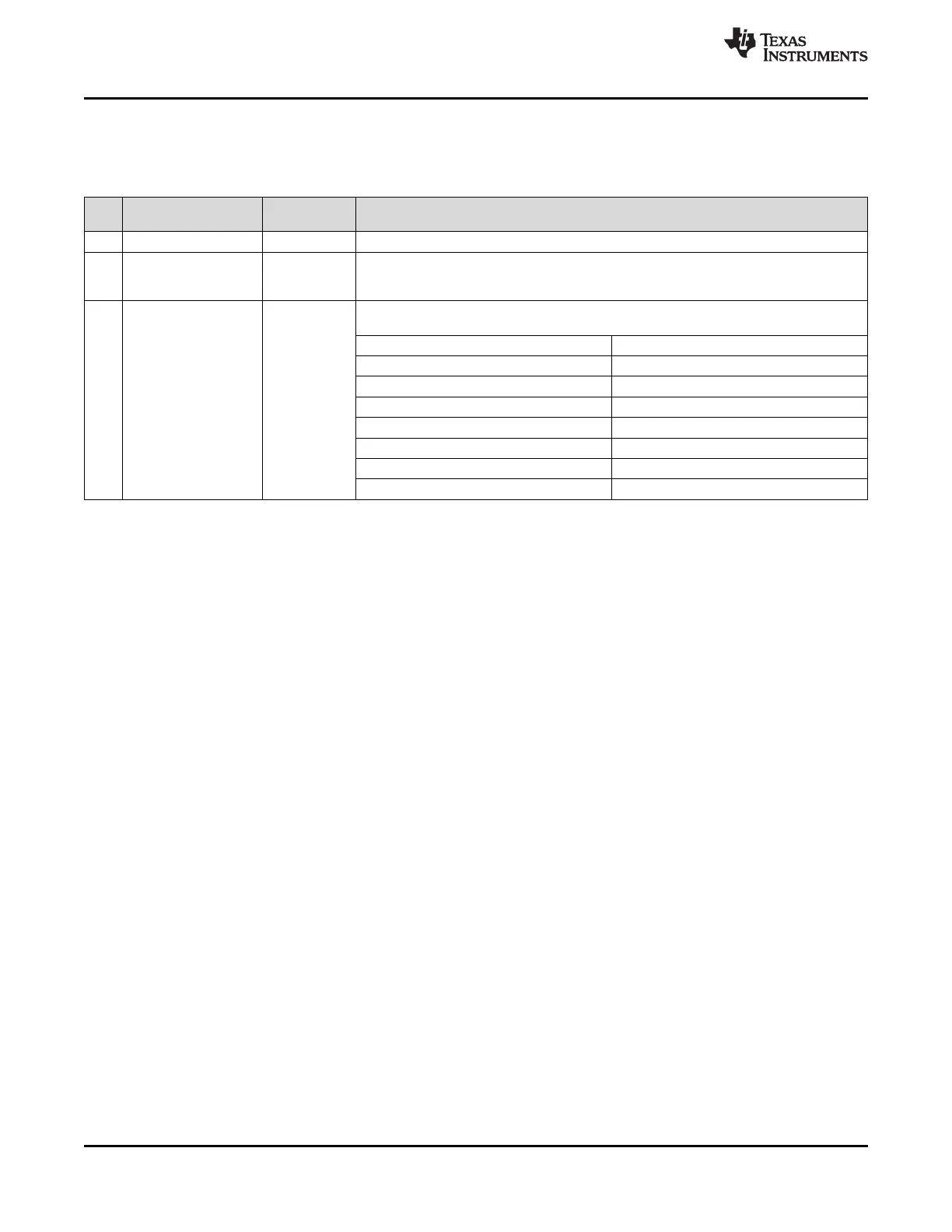

9.7.2.5 SDCLKoutY_ADLY_EN, SDCLKoutY_ADLY

These registers set the analog delay parameters for the SYSREF outputs.

Table 20. Registers 0x105, 0x10D, 0x115, 0x11D, 0x125, 0x12D, 0x135

BIT NAME POR

DESCRIPTION

DEFAULT

7:5 NA 0 Reserved

Enables analog delay for the SYSREF output.

SDCLKoutY

4 0 0: Disabled

_ADLY_EN

1: Enabled

Sets the analog delay value for the SYSREF output. Selecting analog delay adds an

additional 700 ps in propagation delay. Effective range is 700 ps to 2950 ps.

Field Value Delay Value

0 (0x0) 0 ps

1 (0x1) 600 ps

SDCLKoutY

3:0 0

_ADLY 2 (0x2) 750 ps (+150 ps from 0x1)

3 (0x3) 900 ps (+150 ps from 0x2)

... ...

14 (0xE) 2100 ps (+150 ps from 0xD)

15 (0xF) 2250 ps (+150 ps from 0xE)

58 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...