LMK04821

,

LMK04826

,

LMK04828

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

www.ti.com

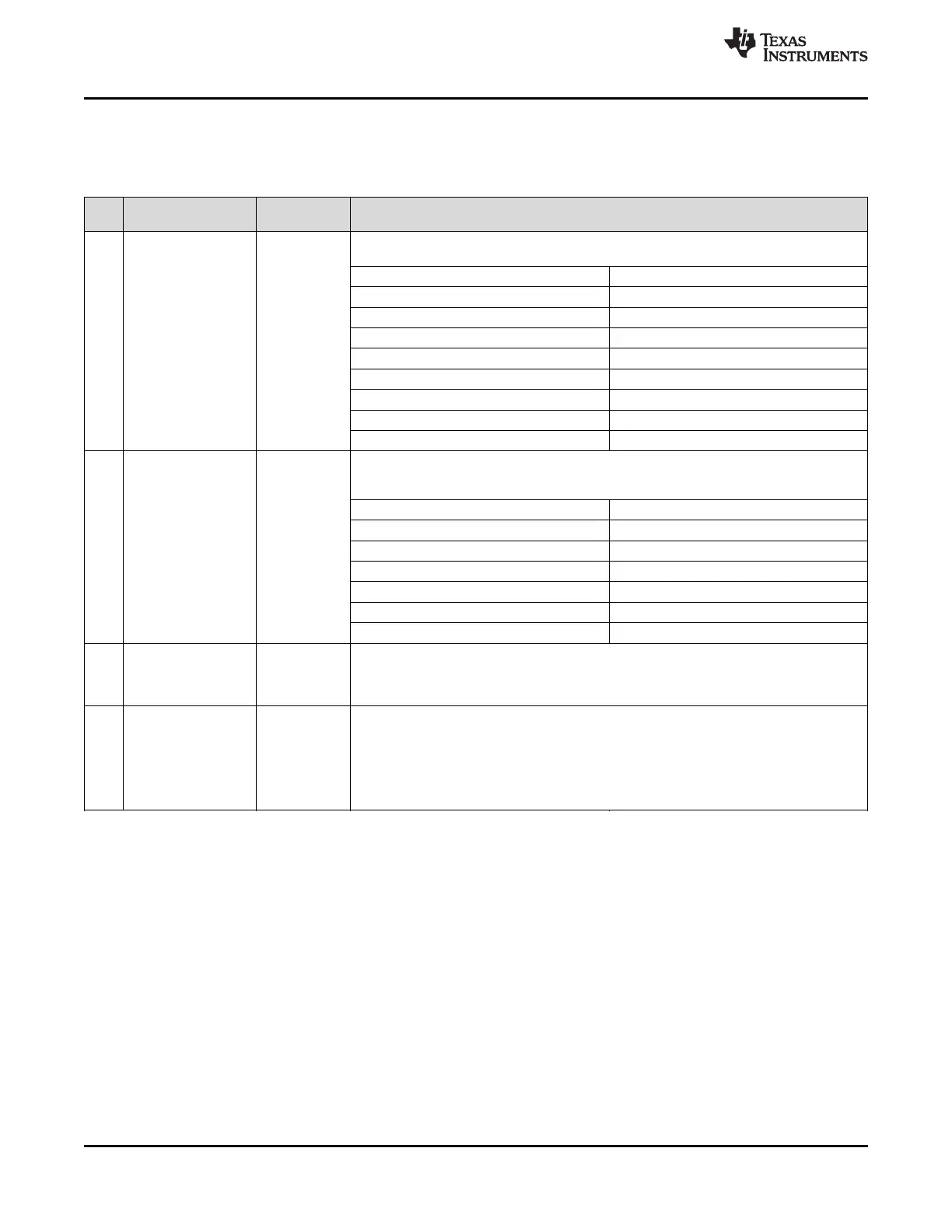

9.7.8.2 PLL2_P, OSCin_FREQ, PLL2_XTAL_EN, PLL2_REF_2X_EN

This register sets other PLL2 functions.

Table 63. Register 0x162

POR

BIT NAME DESCRIPTION

DEFAULT

The PLL2 N Prescaler divides the output of the VCO as selected by Mode_MUX1 and is

connected to the PLL2 N divider.

Field Value Value

0 (0x00) 8

1 (0x01) 2

2 (0x02) 2

7:5 PLL2_P 2

3 (0x03) 3

4 (0x04) 4

5 (0x05) 5

6 (0x06) 6

7 (0x07) 7

The frequency of the PLL2 reference input to the PLL2 Phase Detector (OSCin/OSCin*

port) must be programmed in order to support proper operation of the frequency calibration

routine which locks the internal VCO to the target frequency.

Field Value OSCin Frequency

0 (0x00) 0 to 63 MHz

4:2 OSCin_FREQ 7

1 (0x01) >63 MHz to 127 MHz

2 (0x02) >127 MHz to 255 MHz

3 (0x03) Reserved

4 (0x04) >255 MHz to 500 MHz

5 (0x05) to 7(0x07) Reserved

If an external crystal is being used to implement a discrete VCXO, the internal feedback

amplifier must be enabled with this bit in order to complete the oscillator circuit.

1 PLL2_XTAL_EN 0

0: Oscillator Amplifier Disabled

1: Oscillator Amplifier Enabled

Enabling the PLL2 reference frequency doubler allows for higher phase detector

frequencies on PLL2 than would normally be allowed with the given VCXO or Crystal

frequency.

0 PLL2_REF_2X_EN 1 Higher phase detector frequencies reduces the PLL N values which makes the design of

wider loop bandwidth filters possible.

0: Doubler Disabled

1: Doubler Enabled

84 Submit Documentation Feedback Copyright © 2013–2015, Texas Instruments Incorporated

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...