LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

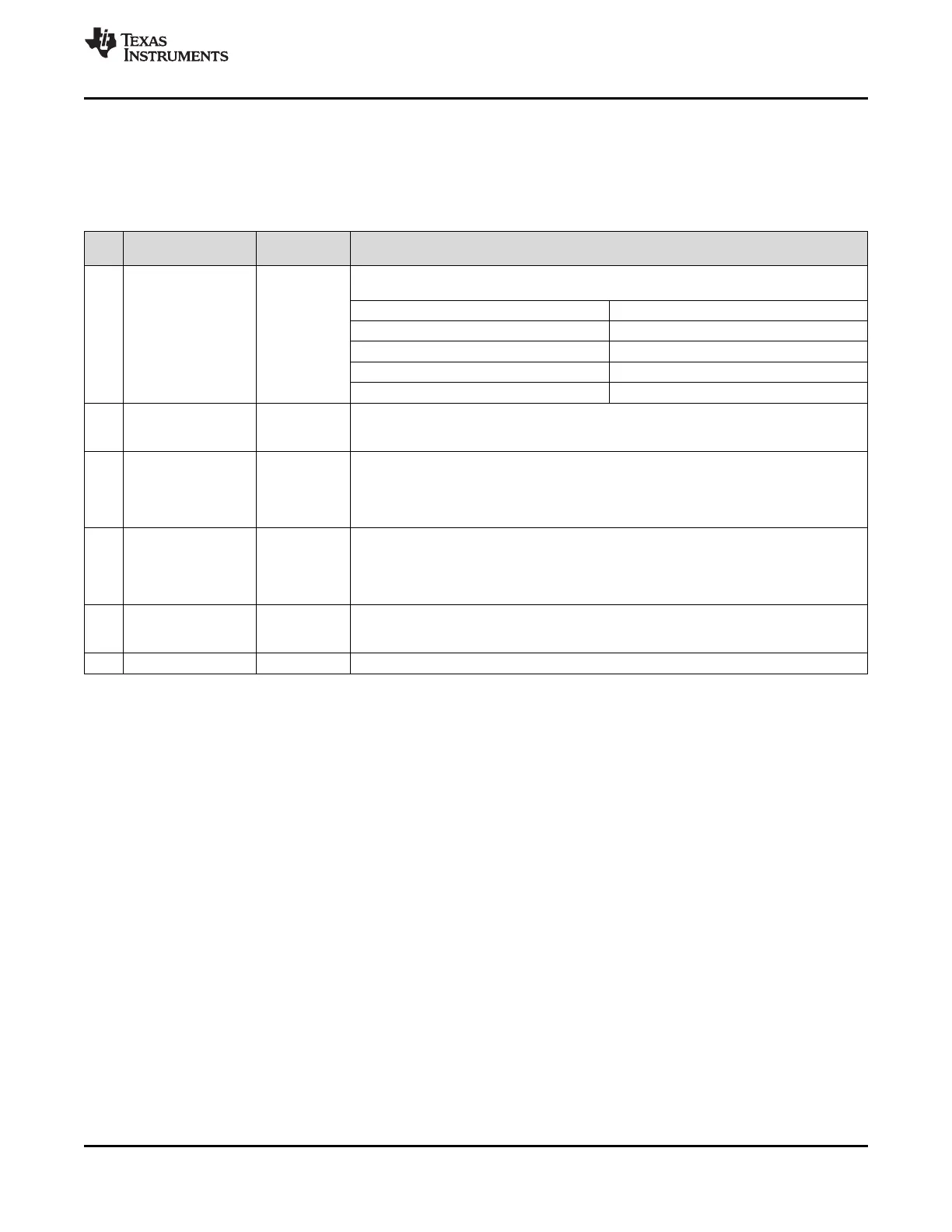

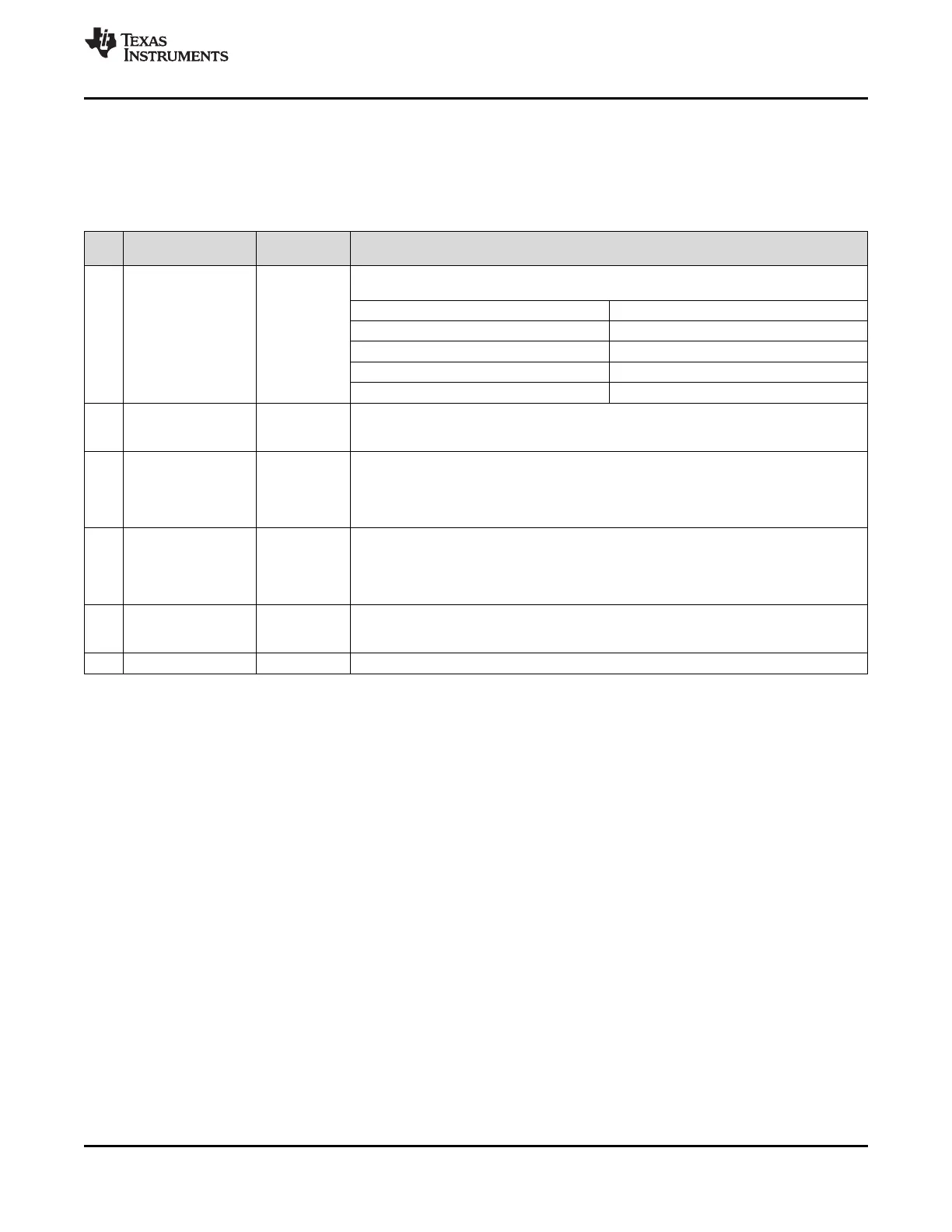

9.7.6 (0x14B - 0x152) Holdover

9.7.6.1 LOS_TIMEOUT, LOS_EN, TRACK_EN, HOLDOVER_FORCE, MAN_DAC_EN, MAN_DAC[9:8]

This register contains the holdover functions.

Table 42. Register 0x14B

POR

BIT NAME DESCRIPTION

DEFAULT

This controls the amount of time in which no activity on a CLKin forces a clock switch

event.

Field Value Timeout

0 (0x00) 370 kHz

7:6 LOS_TIMEOUT 0

1 (0x01) 2.1 MHz

2 (0x02) 8.8 MHz

3 (0x03) 22 MHz

Enables the LOS (Loss-of-Signal) timeout control. Valid for MOS clock inputs.

5 LOS_EN 0 0: Disabled

1: Enabled

Enable the DAC to track the PLL1 tuning voltage, optionally for use in holdover mode. After

device reset, tracking starts at DAC code = 512.

4 TRACK_EN 1 Tracking can be used to monitor PLL1 voltage in any mode.

0: Disabled

1: Enabled, will only track when PLL1 is locked.

This bit forces holdover mode. When holdover mode is forced, if MAN_DAC_EN = 1, then

the DAC will set the programmed MAN_DAC value. Otherwise the tracked DAC value will

HOLDOVER

3 0 set the DAC voltage.

_FORCE

0: Disabled

1: Enabled.

This bit enables the manual DAC mode.

2 MAN_DAC_EN 1 0: Automatic

1: Manual

1:0 MAN_DAC[9:8] 2 See MAN_DAC[9:8], MAN_DAC[7:0] for more information on the MAN_DAC settings.

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 73

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...