LMK04821

,

LMK04826

,

LMK04828

www.ti.com

SNAS605AR –MARCH 2013–REVISED DECEMBER 2015

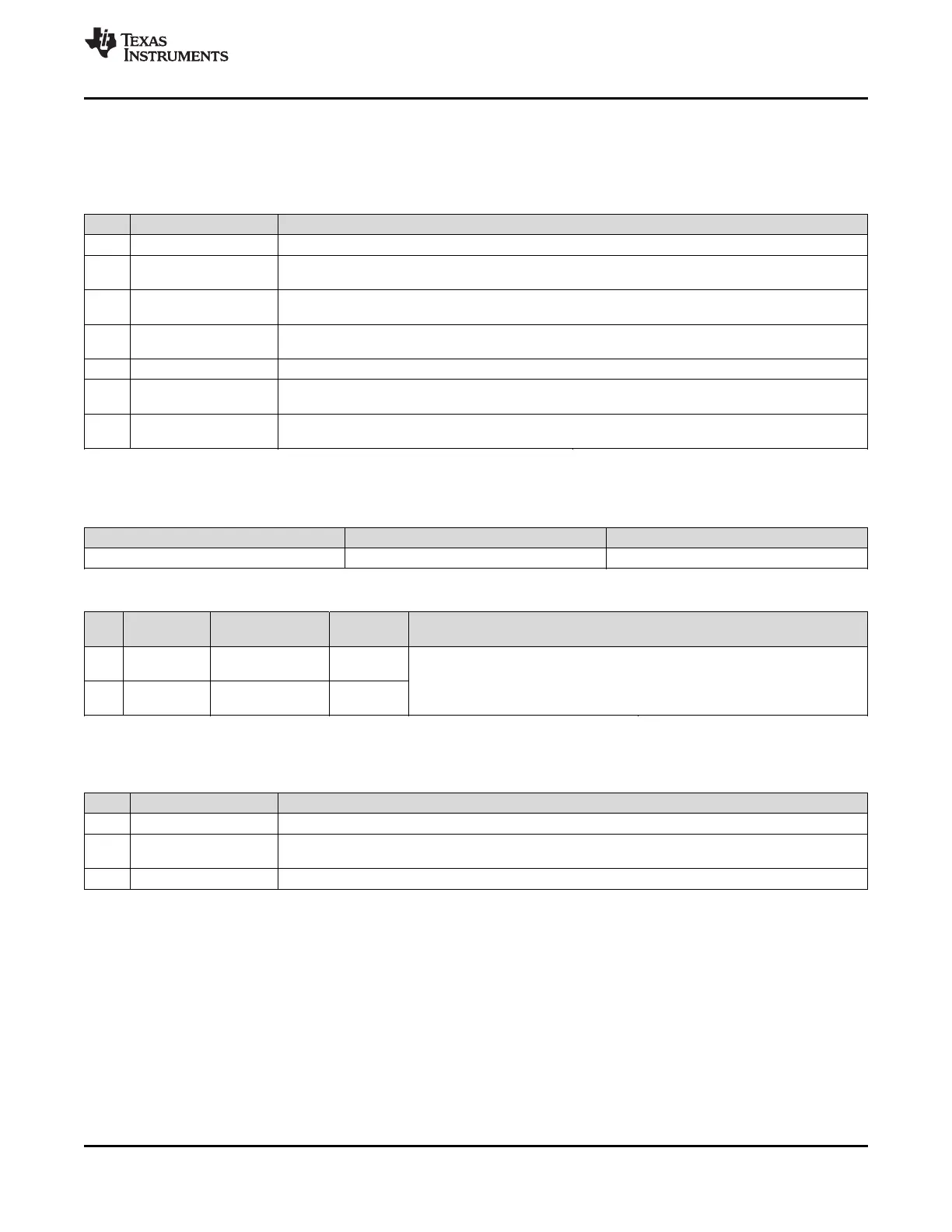

9.7.9.7 RB_DAC_VALUE(MSB), RB_CLKinX_SEL, RB_CLKinX_LOS

This register provides read back access to CLKinX selection indicator and CLKinX LOS indicator. The 2 MSBs

are shared with the RB_DAC_VALUE. See RB_DAC_VALUE section.

Table 80. Register 0x184

BIT NAME DESCRIPTION

7:6 RB_DAC_VALUE[9:8] See RB_DAC_VALUE section.

Read back 0: CLKin2 is not selected for input to PLL1.

5 RB_CLKin2_SEL

Read back 1: CLKin2 is selected for input to PLL1.

Read back 0: CLKin1 is not selected for input to PLL1.

4 RB_CLKin1_SEL

Read back 1: CLKin1 is selected for input to PLL1.

Read back 0: CLKin0 is not selected for input to PLL1.

3 RB_CLKin0_SEL

Read back 1: CLKin0 is selected for input to PLL1.

2 N/A

Read back 1: CLKin1 LOS is active.

1 RB_CLKin1_LOS

Read back 0: CLKin1 LOS is not active.

Read back 1: CLKin0 LOS is active.

0 RB_CLKin0_LOS

Read back 0: CLKin0 LOS is not active.

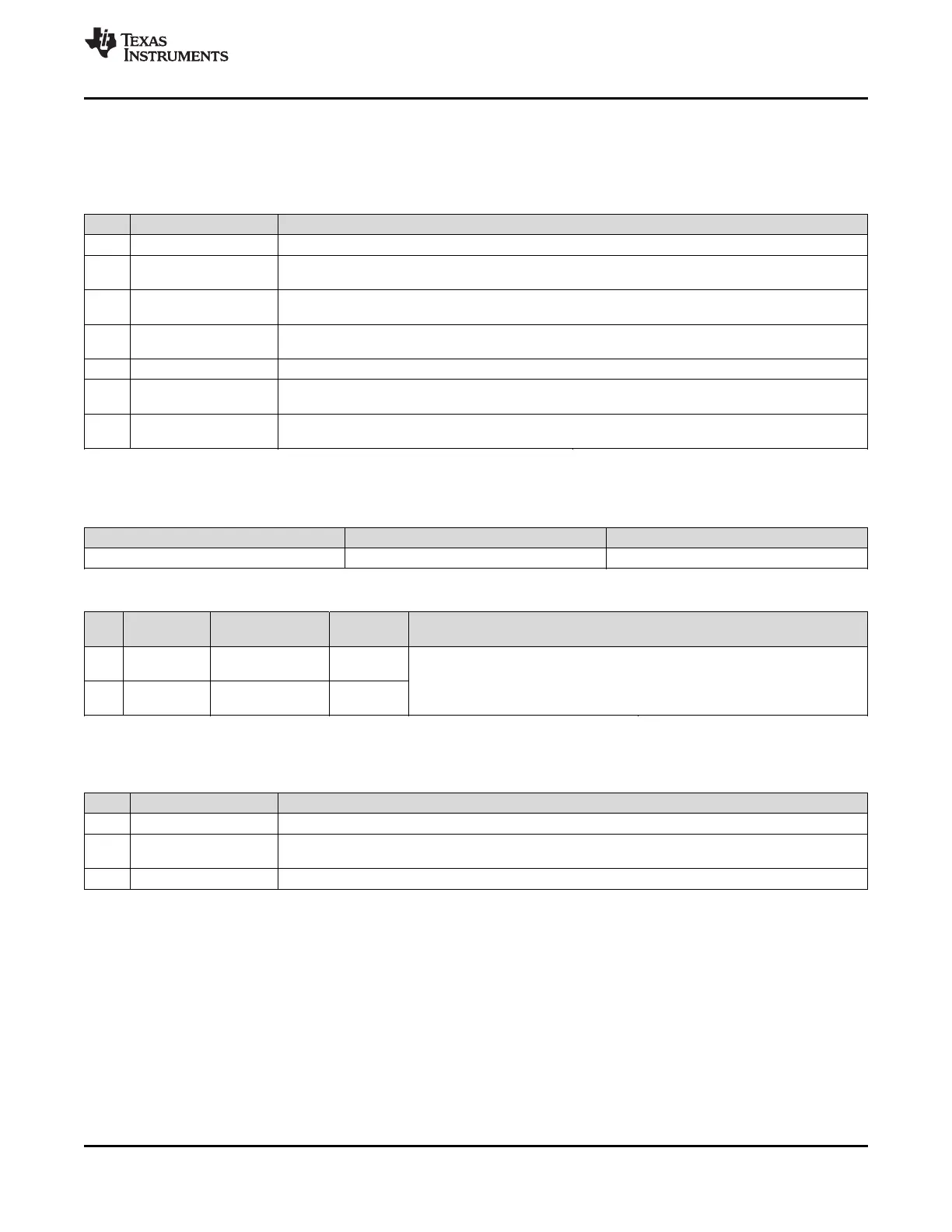

9.7.9.8 RB_DAC_VALUE

Contains the value of the DAC for user readback.

FIELD NAME MSB LSB

RB_DAC_VALUE 0x184 [7:6] 0x185 [7:0]

Table 81. Registers 0x184 and 0x185

POR

BIT REGISTERS NAME DESCRIPTION

DEFAULT

RB_DAC_ DAC value is 512 on power on reset, if PLL1 locks upon power-up the DAC

7:6 0x184 2

VALUE[9:8] value will change.

RB_DAC_

7:0 0x185 0

VALUE[7:0]

9.7.9.9 RB_HOLDOVER

Table 82. Register 0x188

BIT NAME DESCRIPTION

7:5 N/A Reserved

Read back 0: Not in HOLDOVER.

4 RB_HOLDOVER

Read back 1: In HOLDOVER.

3:0 N/A Reserved

Copyright © 2013–2015, Texas Instruments Incorporated Submit Documentation Feedback 93

Product Folder Links: LMK04821 LMK04826 LMK04828

Loading...

Loading...