Advisory ADC: 12-Bit Input Capacitance When Switching Channel Groups

Revisions Affected

0, A, B

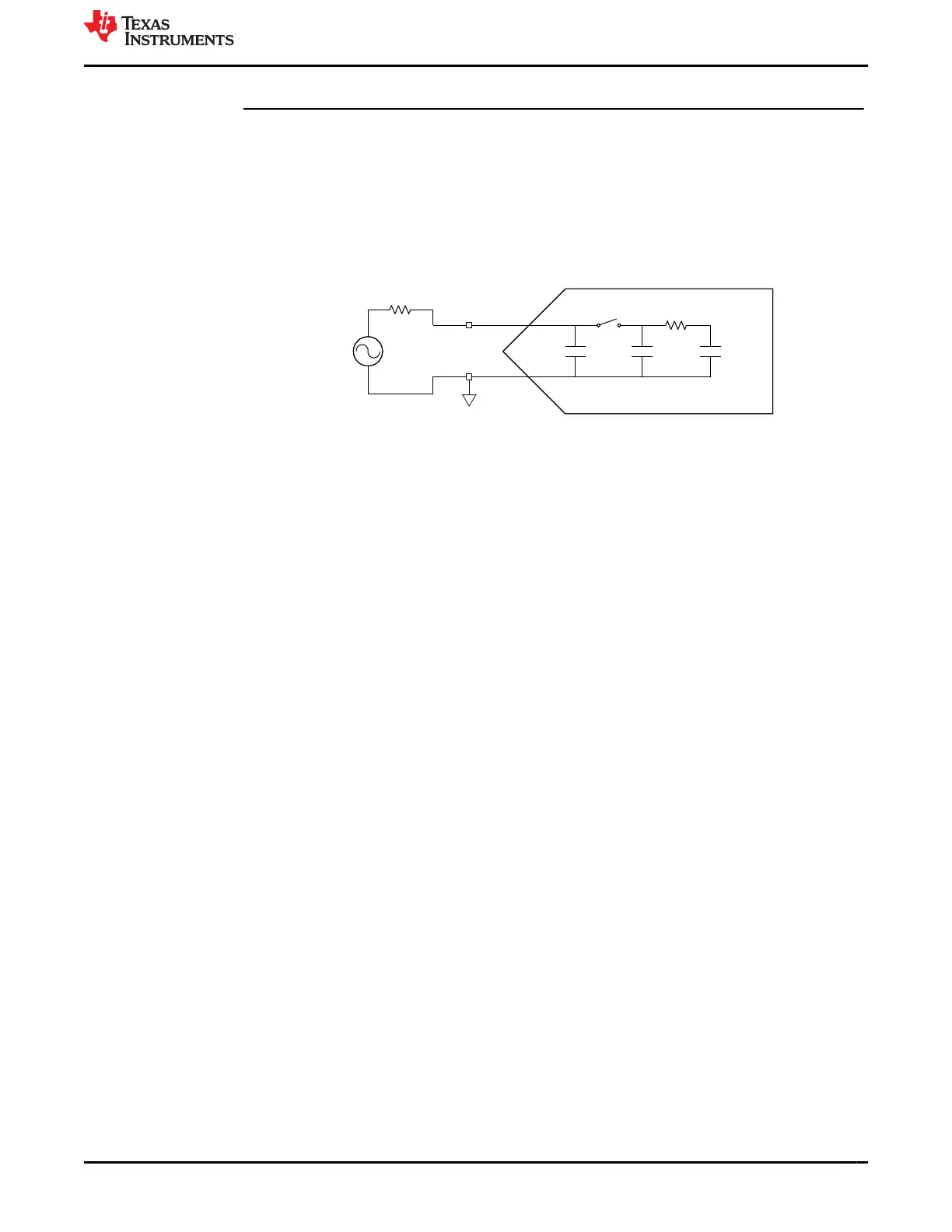

Details The ADC input model should be used to select the sample-and-hold (S+H) duration for

each ADC input. For the revisions affected, if the currently converting channel is an

even-numbered channel and the previously converted channel was an odd-numbered

channel (or vice versa), then the 12-bit input model will not accurately predict ADC input

performance. Under these conditions, an additional capacitance should be added to the

model. This capacitance has a value of 11.5 pF and should be placed between the S+H

switch and R

on

as shown in Figure 4-1.

AC

ADCINx

ADC

11.5 pF

Switch

R

s

R

on

C

p

C

h

V

REFLO

Figure 4-1. Single-Ended Input Model

Workarounds For the revisions affected, when subsequent conversions switch between channel groups,

the S+H duration should be chosen to account for the additional capacitance.

www.ti.com Silicon Revision B Usage Notes and Advisories

SPRZ412M – DECEMBER 2013 – REVISED MARCH 2023

Submit Document Feedback

TMS320F2837xD Dual-Core Real-Time MCUs Silicon Errata (Silicon

Revisions C, B, A, 0)

41

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...