KC705 Getting Started Guide www.xilinx.com 31

UG883 (v4.0.1) May 28, 2014

Advanced Bring-up Using the Base Targeted Reference Design

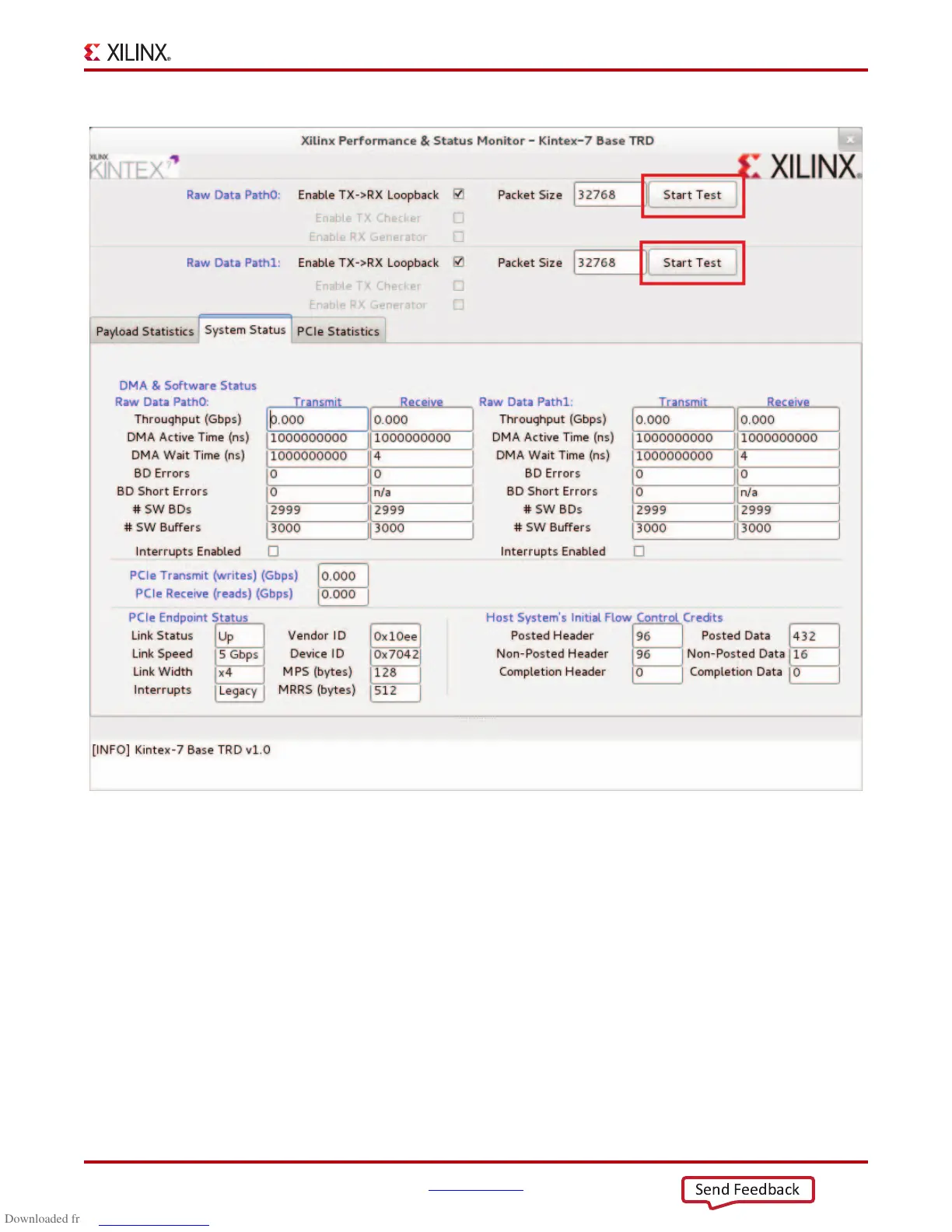

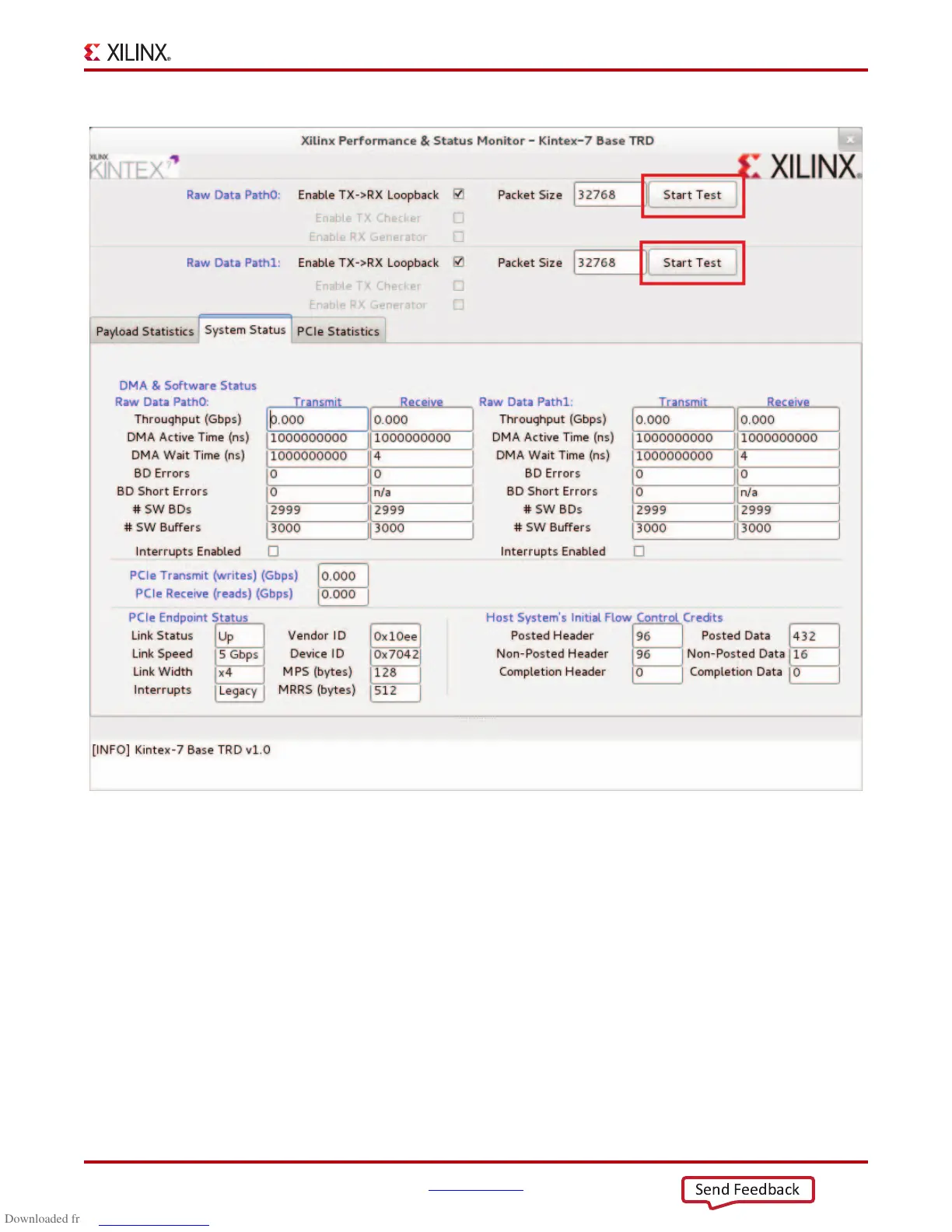

3. Verify TRD operations through the status information provided by the GUI (see

Figure 21).

a. Verify the PCIe throughput.

b. Verify the DMA channel throughput for the Raw Data Path0.

c. Verify the DMA channel throughput for the Raw Data Path1.

d. Verify there are no buffer descriptor errors for error-free operation.

X-Ref Target - Figure 20

Figure 20: Start Data Traffic from the Performance Monitor

UG883_20_121112

Loading...

Loading...