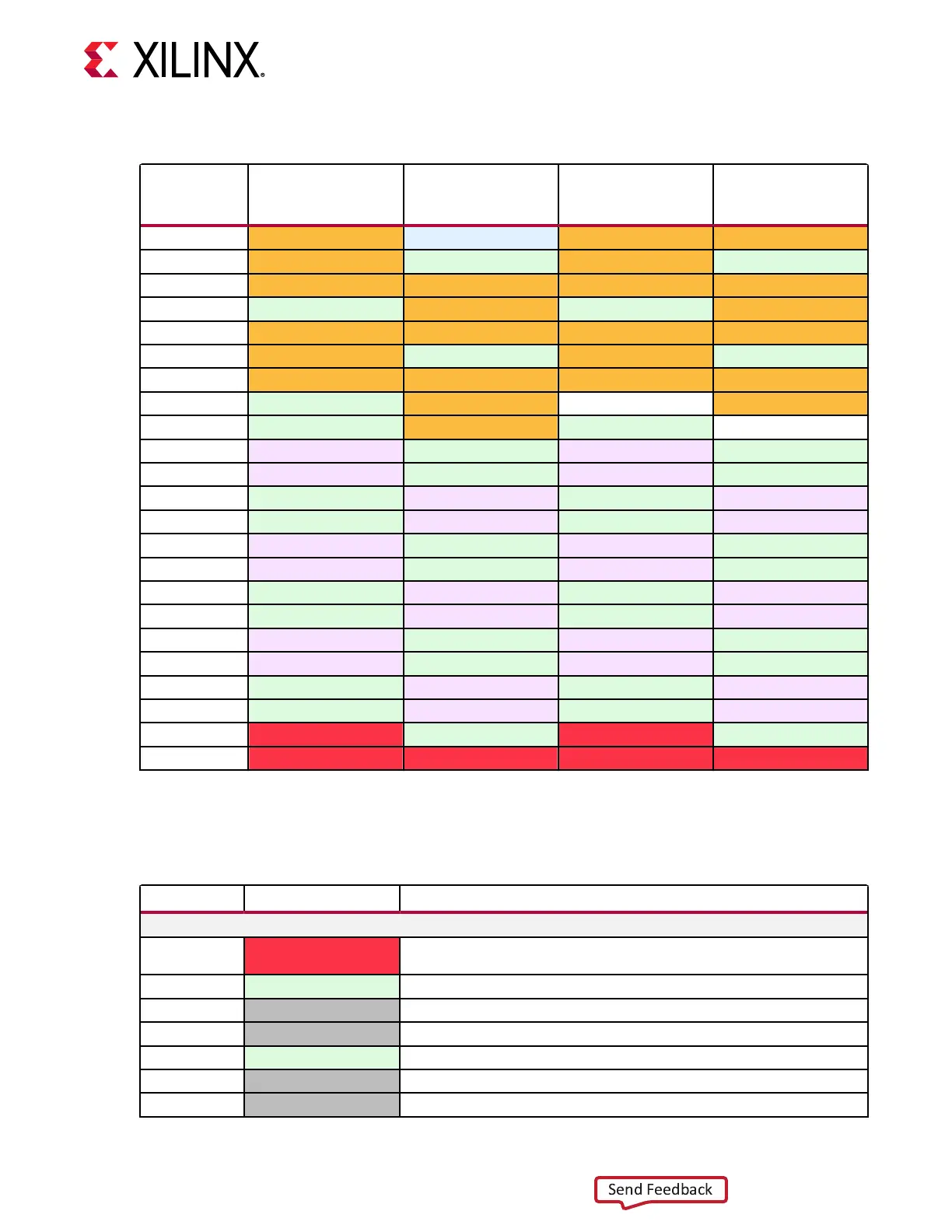

Table 3: SOM240_1 Connector Pinout (cont'd)

Connector

Row/ Pin

Number

A B C D

38 MIO61 Reserved MIO55 MIO54

39 MIO62 GND MIO56 GND

40 MIO63 MIO58 MIO57 MIO64

41 GND MIO59 GND MIO65

42 MIO73 MIO60 MIO67 MIO66

43 MIO74 GND MIO68 GND

44 MIO75 MIO70 MIO69 MIO76

45 GND MIO71 Reserved MIO77

46 GND MIO72 GND Reserved

47 GTR_DP1_M2C_P GND GTR_REFCLK0_C2M_P GND

48 GTR_DP1_M2C_N GND GTR_REFCLK0_C2M_N GND

49 GND GTR_REFCLK1_C2M_P GND GTR_DP3_C2M_P

50 GND GTR_REFCLK1_C2M_N GND GTR_DP3_C2M_N

51 GTR_REFCLK3_C2M_P GND GTR_DP3_M2C_P GND

52 GTR_REFCLK3_C2M_N GND GTR_DP3_M2C_N GND

53 GND GTR_DP2_C2M_P GND GTR_REFCLK2_C2M_P

54 GND GTR_DP2_C2M_N GND GTR_REFCLK2_C2M_N

55 GTR_DP0_C2M_P GND GTR_DP1_C2M_P GND

56 GTR_DP0_C2M_N GND GTR_DP1_C2M_N GND

57 GND GTR_DP0_M2C_P GND GTR_DP2_M2C_P

58 GND GTR_DP0_M2C_N GND GTR_DP2_M2C_N

59 VCC_SOM GND VCC_SOM GND

60 VCC_SOM VCC_SOM VCC_SOM VCC_SOM

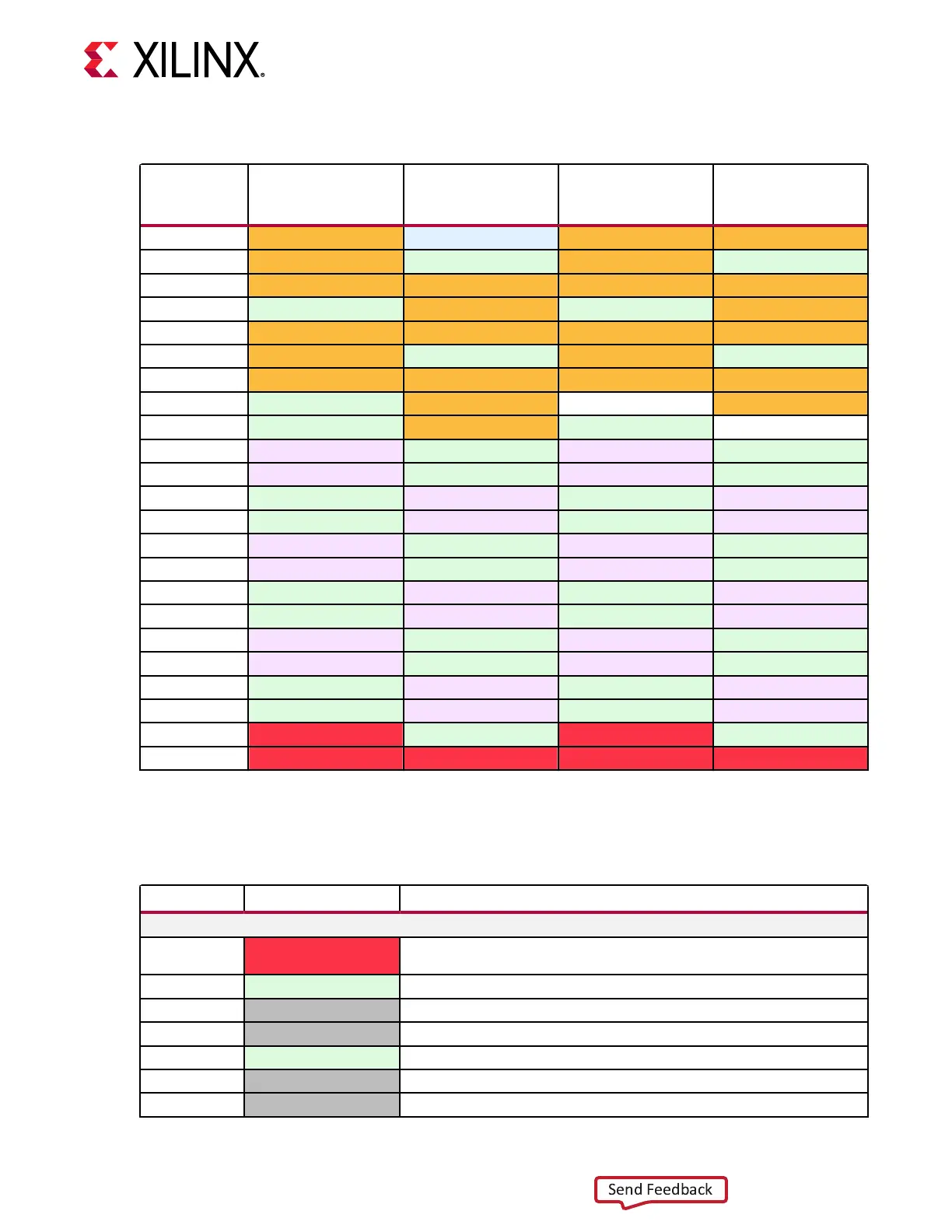

SOM240_1 Signal Names and Descriptions

Table 4: SOM240_1 Signal Pins

Pin Number Signal Name Signal Description

Connector Row A

A1 VCC_BATT PS BBRAM and real-time clock (RTC) supply voltage, requires external battery.

Connect to GND when battery is not used.

A2 GND Ground

A3 HPA06_P HPIO on bank 66

A4 HPA06_N HPIO on bank 66

A5 GND Ground

A6 HPA_CLK0_P HPIO global clock pin on bank 66

A7 HPA_CLK0_N HPIO global clock pin on bank 66

Chapter 2: Electrical Design Considerations

UG1091 (v1.0) April 20, 2021 www.xilinx.com

Carrier Card Design for Kria SOM 10

Loading...

Loading...