18 www.xilinx.com Spartan-6 FPGA Power Management

UG394 (v1.1) September 4, 2012

Chapter 1: Power Management With Suspend Mode

•The sw_clk option is specific to the suspend feature. By default,

sw_clk:InternalClk.

•The StartupClk option is available on every application. The same option used to

clock the start-up process at the end of configuration can be used to clock the wake-up

process at the end of suspend. StartupClk:Cclk is the default; however, using this

for suspend wake-up requires a persisted slave configuration mode. When using

sw_clk:StartupClk and StartupClk:Cclk, and exiting suspend mode, the

CCLK pin becomes the clock source. The Persist option also retains the dual-purpose

configuration pins associated with the configuration logic.

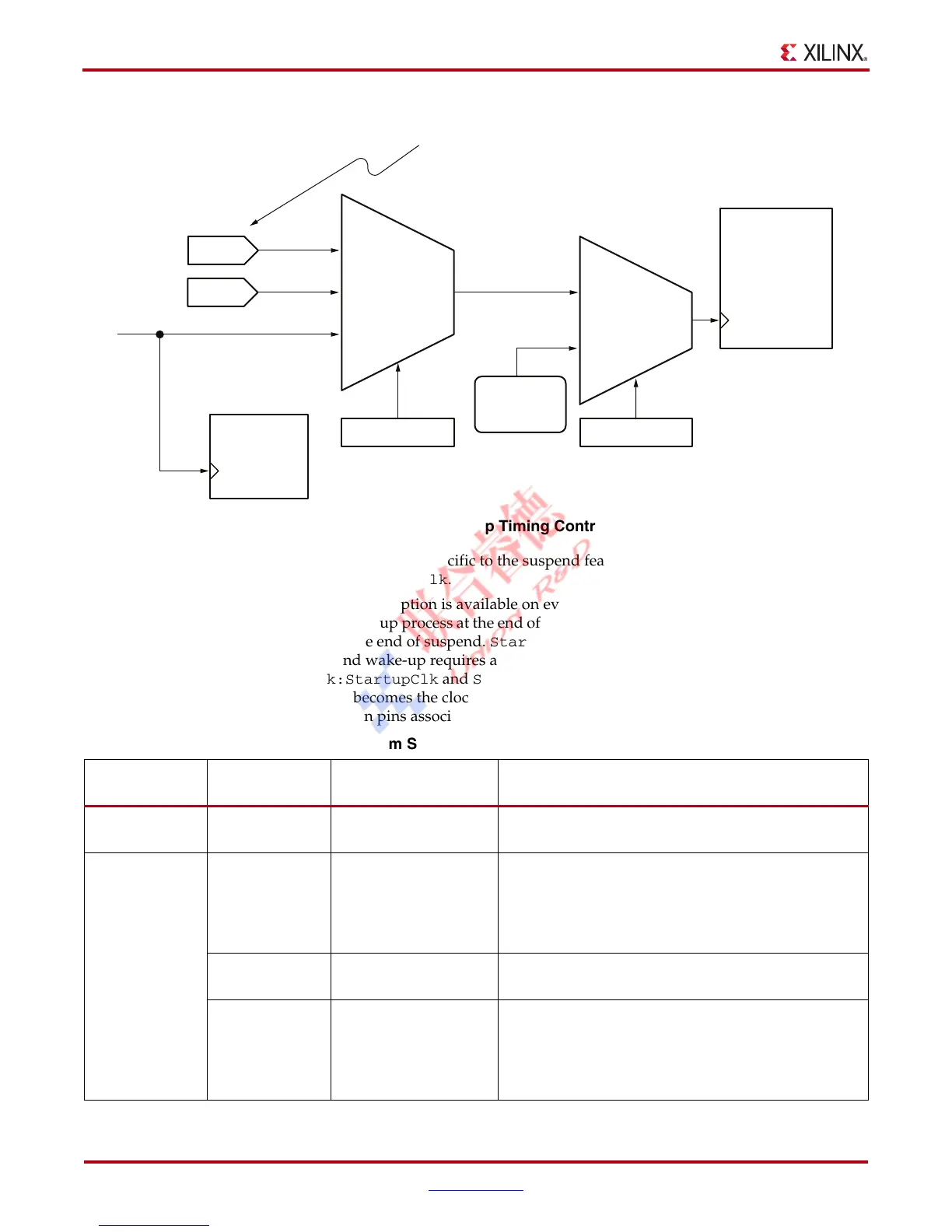

X-Ref Target - Figure 1-4

Figure 1-4: Suspend Mode Wake-Up Timing Control Clock Selection

StartupClk

InternalClk

sw_clk

~50 MHz

Internal

Oscillator

Cclk

Jtag

UserClk

CCLK

TCK

STARTUP_SPARTAN6

StartupClk

CLK

CCLK input only available for

applications that configure in Slave

mode. Persist = Yes required.

User Clock from

FPGA Interconnect

Suspend

Wake-Up

Timing

Control

UG394_c1_04_121009

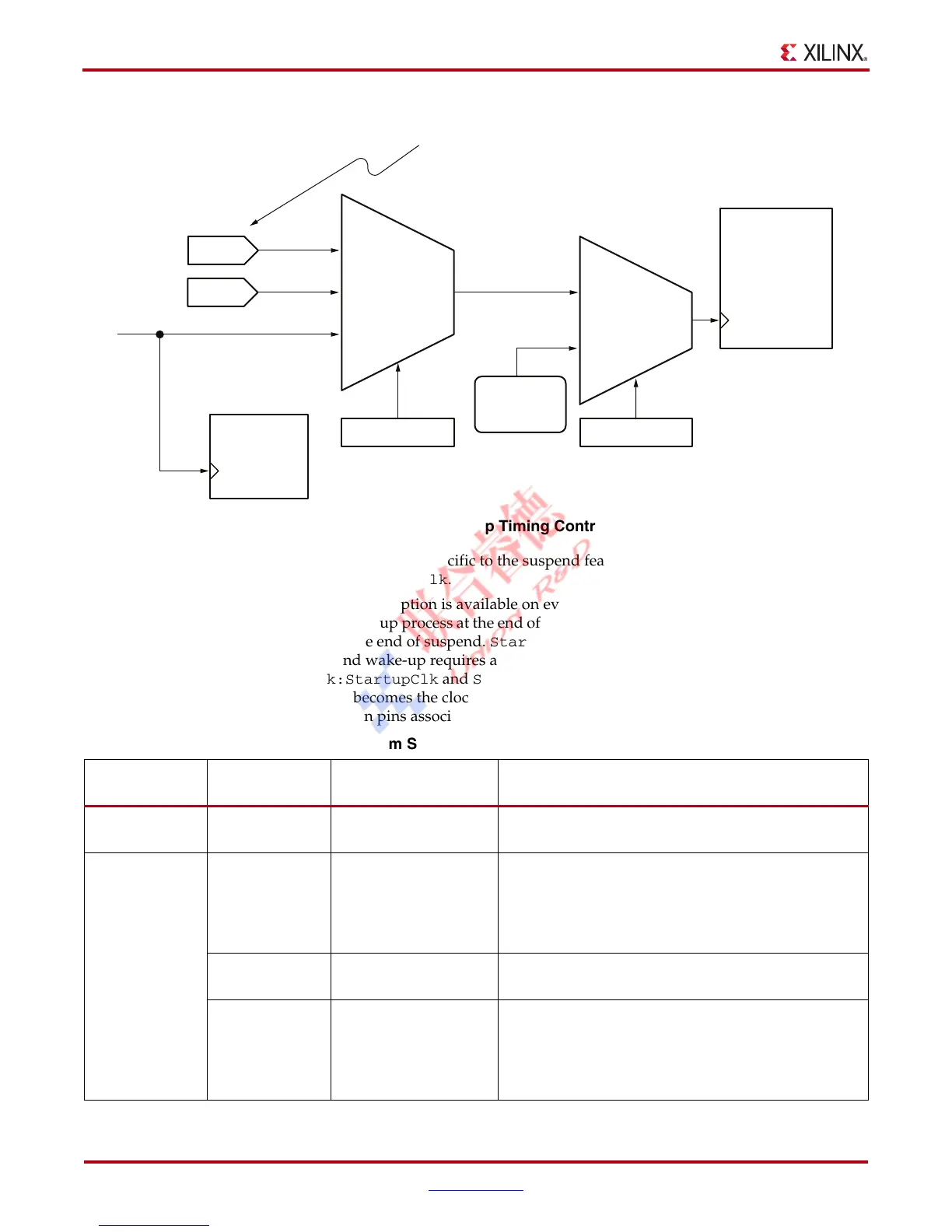

Table 1-3: Clock Sources to Wake-Up from Suspend Mode

sw_clk

Setting

StartupClk

Setting

Clock Source Restriction

InternalClk NA Internal Oscillator

The oscillator has an imprecise frequency of about

50 MHz.

StartupClk

Cclk CCLK pin on FPGA

This option is only available for FPGAs using Slave

configuration mode. The bitstream option Persist:Yes

must be set. This option is not available for FPGAs

using the master configuration mode; use InternalClk

instead.

JtagClk TCK pin on FPGA

The JTAG interface must be active to exit suspend

mode.

UserClk

CLK input on the

STARTUP_SPARTAN6

design primitive

The clock input to the STARTUP design primitive can

originate from any non-clocked signal in the FPGA. It

cannot originate from a flip-flop source because all

clocked primitives are write-protected while in

suspend mode.

Loading...

Loading...