Spartan-6 FPGA Power Management www.xilinx.com 31

UG394 (v1.1) September 4, 2012

Chapter 4

Power-On and Power-Down Behavior

Including Hibernate

Introduction

Spartan-6 FPGAs are designed for maximum system flexibility and reliability when

powering up and powering down. During power-on, the device ensures reliable

configuration by waiting until a fixed time after the supply rails are valid. During

power-down or hibernate, the device disables the outputs and awaits re-application of

power to reconfigure. Both power-up and power-down are enhanced by the hot swap

compliance of the I/O, allowing the FPGA to be moved in or out of a powered system

without damage.

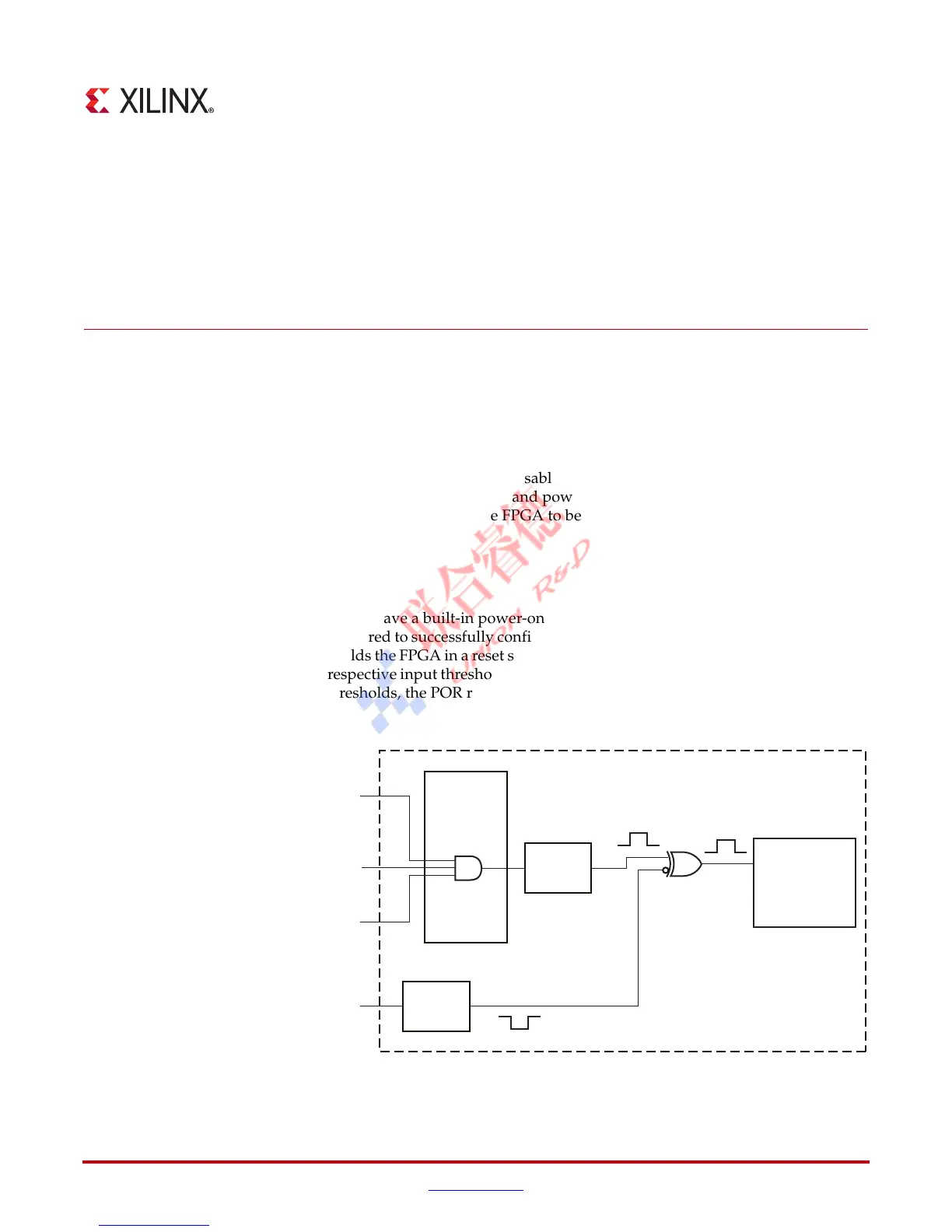

Power-On Reset

Spartan-6 FPGAs have a built-in power-on reset (POR) circuit that monitors the three

power rails required to successfully configure the FPGA (see Figure 4-1). At power-up, the

POR circuit holds the FPGA in a reset state until the V

CCINT

, V

CCAUX

, and V

CCO_2

supplies

reach their respective input threshold levels. A time t

POR

after all three supplies reach their

respective thresholds, the POR reset is released and the FPGA begins its configuration

process.

X-Ref Target - Figure 4-1

Figure 4-1: Simplified POR Circuit Diagram

Spartan-6 FPGA

Reset

Glitch

Filter

PROGRAM_B

V

CCO_2

V

CCAUX

V

CCINT

Power-On

Reset

Configuration

Logic

Glitch

Filter

UG394_c4_01_022210

Loading...

Loading...