20 www.xilinx.com Spartan-6 FPGA Power Management

UG394 (v1.1) September 4, 2012

Chapter 1: Power Management With Suspend Mode

Do not use any other JTAG instructions when in suspend mode or while transitioning into

and out of suspend mode. Furthermore, do not enter suspend mode when performing a

readback operation.

SUSPEND Pin

When the suspend feature is enabled (see Enable the Suspend Feature and Glitch Filtering,

page 14), the SUSPEND pin controls when the FPGA enters suspend mode. During normal

FPGA operation, the SUSPEND pin must be Low. When High, the SUSPEND pin forces the

FPGA into the low-power suspend mode. Table 1-5 describes the functionality of the

SUSPEND pin.

If the suspend feature is not enabled for an application (the application never enters

low-power mode), then connect the SUSPEND pin to GND. Do not leave the pin floating

or High.

Characteristics

The SUSPEND pin is an LVCMOS/LVTTL receiver, and power to the input buffer is

supplied by the V

CCAUX

power rail. The SUSPEND pin has no pull-up resistors during

configuration, and the HSWAPEN control has no effect on the SUSPEND pin.

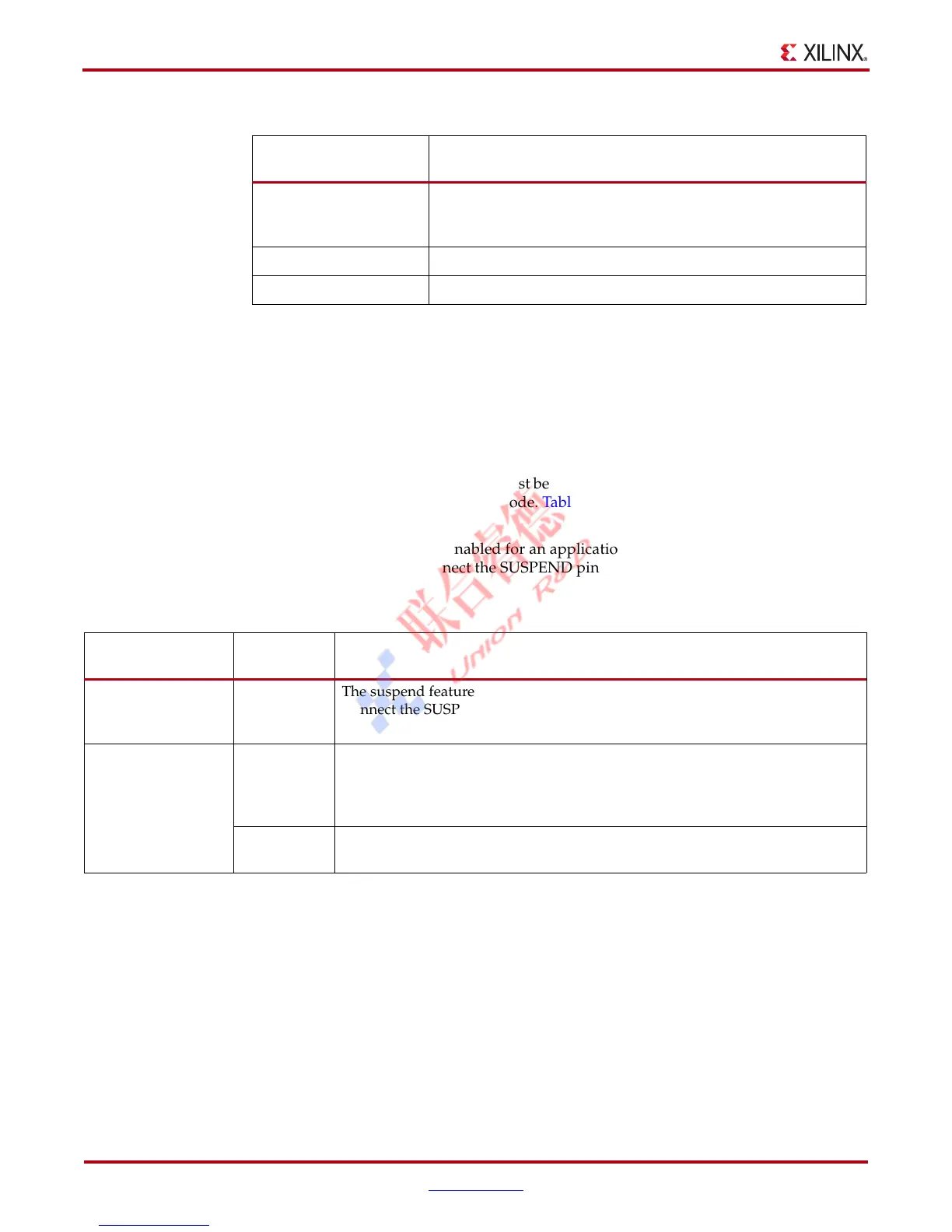

Table 1-4: JTAG Operations Allowed during Suspend Mode

Boundary-Scan

Command

Description

IDCODE

Read the JTAG ID code that describes the Spartan-6 FPGA array

type in the JTAG chain. This value is different from the Device

DNA identifier, which is unique to every device.

BYPASS Enables BYPASS.

USERCODE Read the user-defined code embedded in the FPGA bitstream.

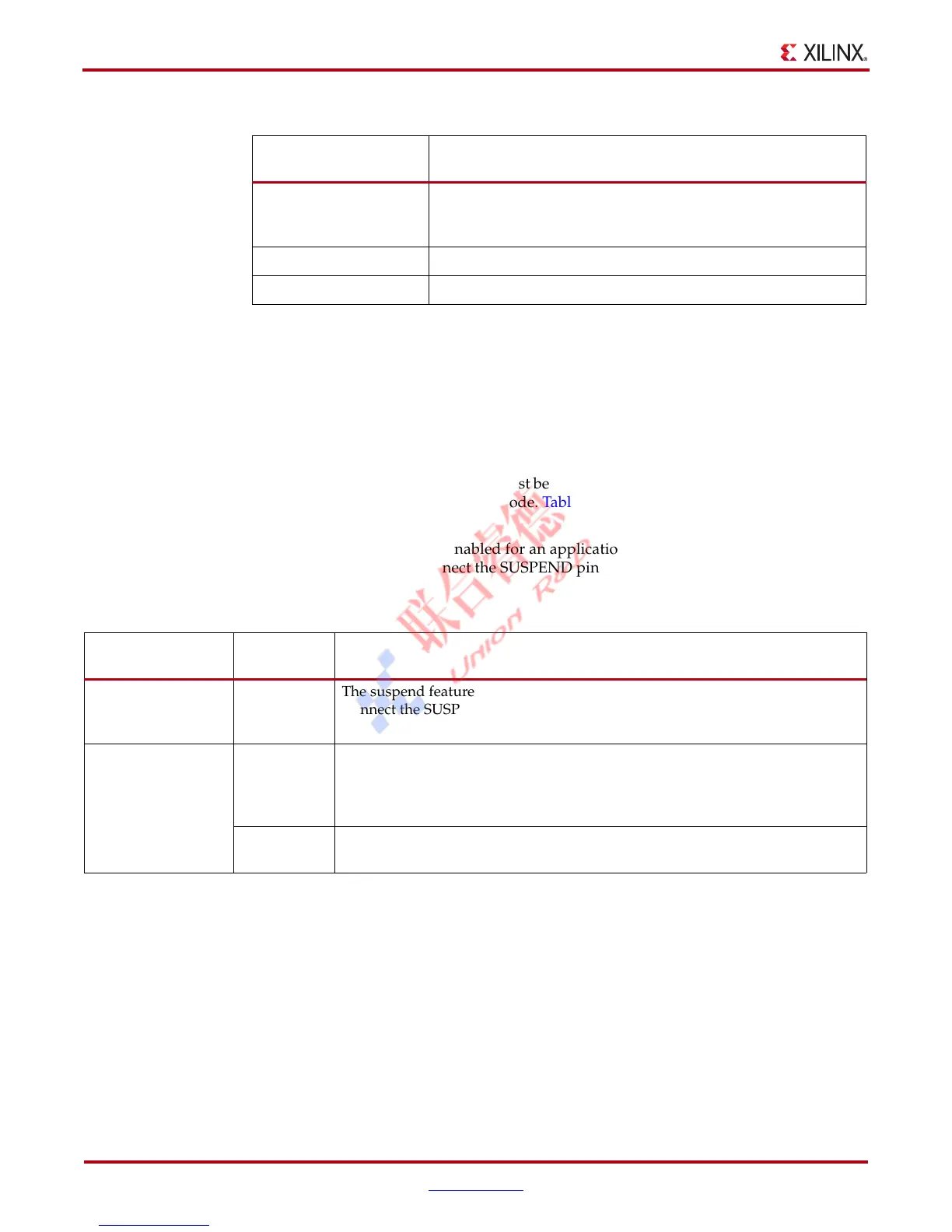

Table 1-5: SUSPEND Pin Functionality

ENABLE_SUSPEND

Settings

SUSPEND

Pin

Function

NO (default)

Suspend Mode

Disabled

0

The suspend feature is disabled. The SUSPEND pin is unused and ignored.

Connect the SUSPEND pin to GND.

Filtered, Unfiltered

Suspend Mode

Enabled

0

The FPGA performs the application described in the bitstream loaded into the

FPGA during configuration. When the SUSPEND pin changes from High to

Low, wake the FPGA from suspend mode. Return from suspend mode also

depends on the SCP pins, if used.

1

Force the FPGA to enter power-saving suspend mode pending SACK assertion

on SUSPEND_SYNC primitive, if used.

Loading...

Loading...