Spartan-6 FPGA Power Management www.xilinx.com 35

UG394 (v1.1) September 4, 2012

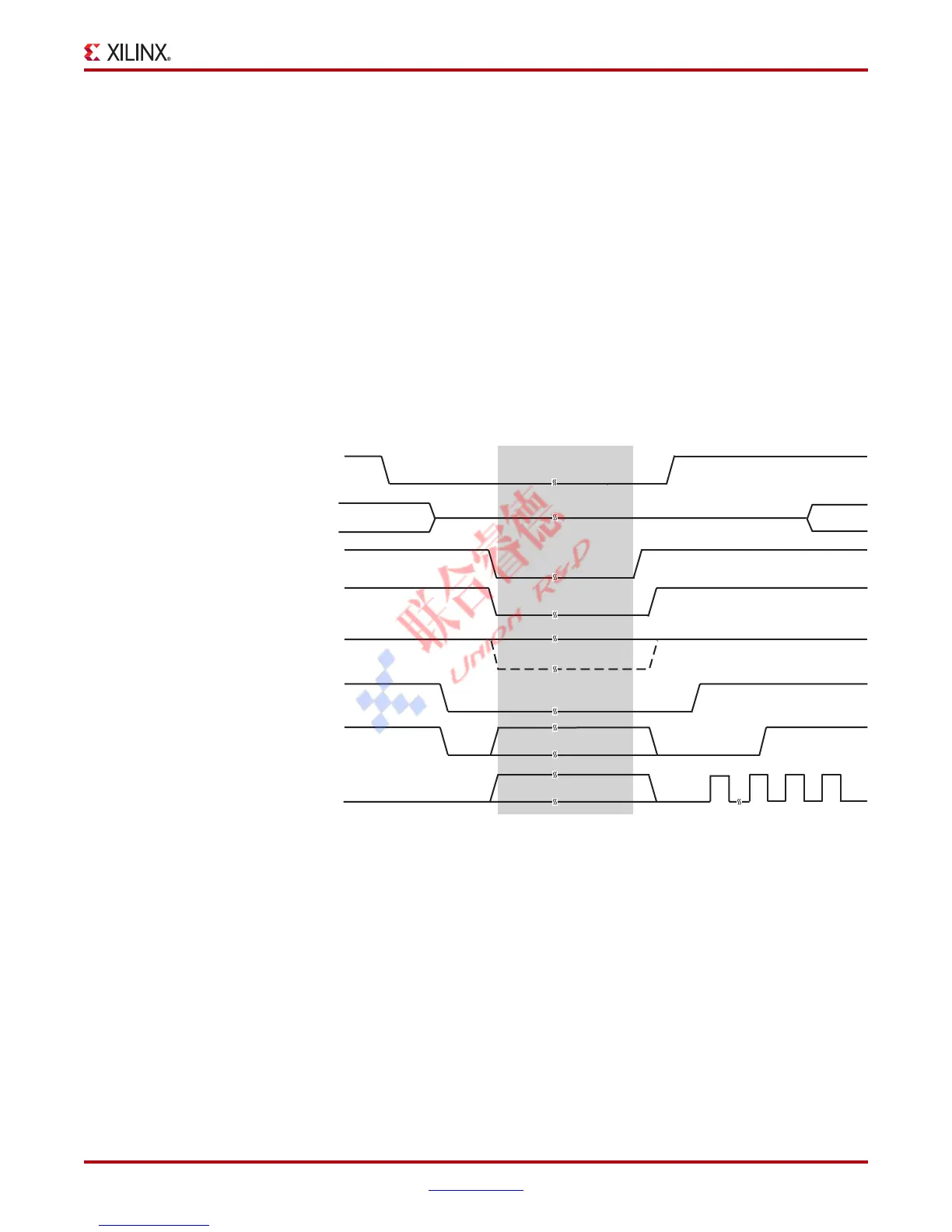

Hibernate Power Down

Turn Off V

CCO

Spartan-6 FPGA I/O pins have a floating-well structure, providing full hot-swap/

hot-insertion capability. When a Spartan-6 FPGA is in the Hibernate state, the V

CCO

supply

can be safely turned off without adversely affecting either the FPGA or the external

application. When entering the Hibernate state, V

CCO

should be turned off first to disable

the outputs without any unwanted transitions.

Figure 4-3 shows the waveforms for entering and exiting Hibernate. The steps for entering

Hibernate are as follows:

1. Pull the PROGRAM_B pin Low to force all user-I/O pins into a high-impedance state.

2. The FPGA drives the INIT_B and DONE pins Low.

3. External switches turn off the V

CCINT

, V

CCAUX

, and V

CCO

supply rails to the FPGA.

4. The FPGA is now in Hibernate. While the FPGA is kept in this state, power

consumption rests at the lowest possible level.

X-Ref Target - Figure 4-3

Figure 4-3: Hibernate Waveform

PROGRAM_B

I/Os

V

CCINT

V

CCAUX

V

CCO

(per I/O Bank)

INIT_B

DONE

CCLK

Undefined

in Master Mode

UG394_c4_03_111309

Hibernate

Undefined

STARTUP cycles

Loading...

Loading...