Zynq UltraScale+ VCU TRD User Guide 74

UG1250 (v2019.1) May 29, 2019 www.xilinx.com

Chapter 5: Hardware Platform

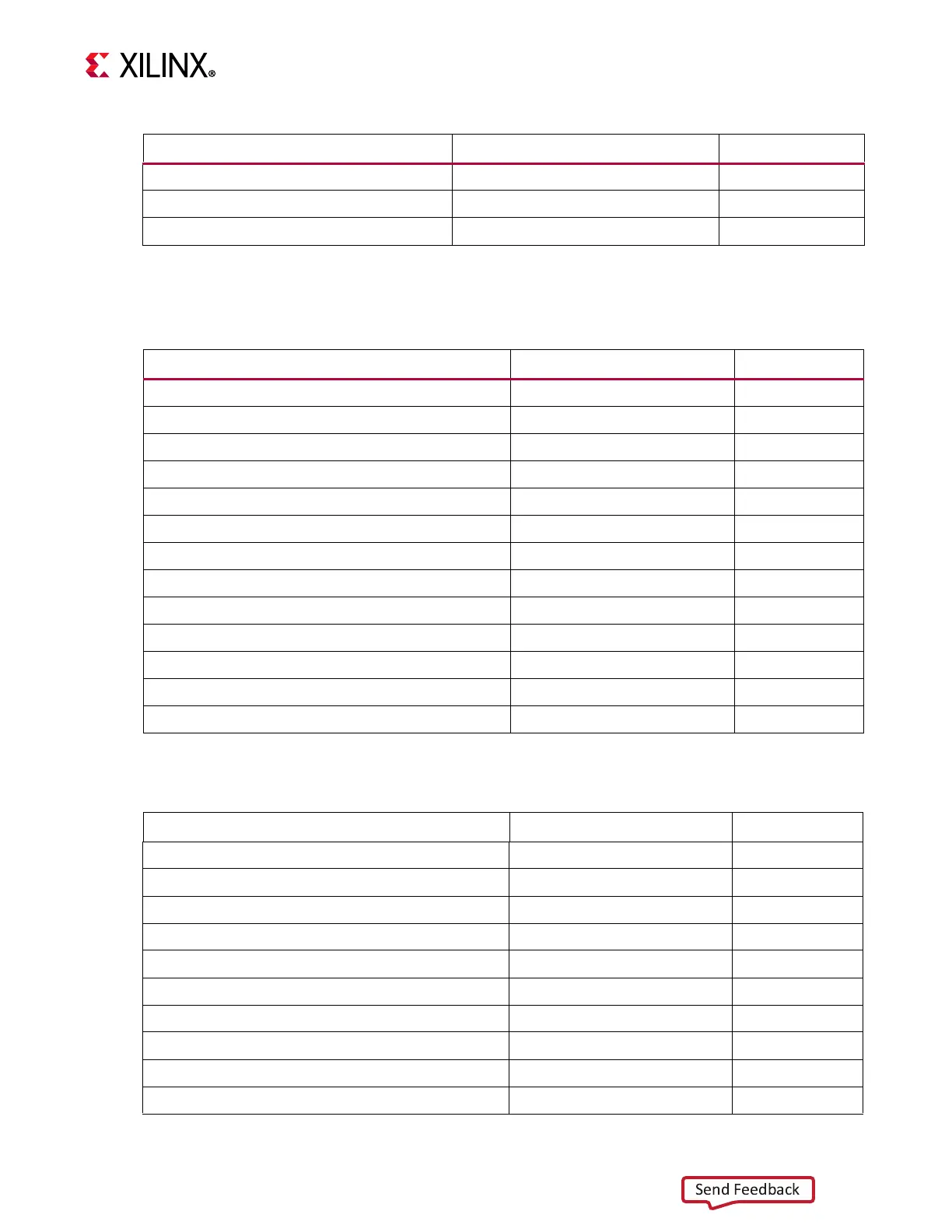

Tab le 5 -3 shows the address map of various IP blocks used in the PL of an Ethernet 10G

design.

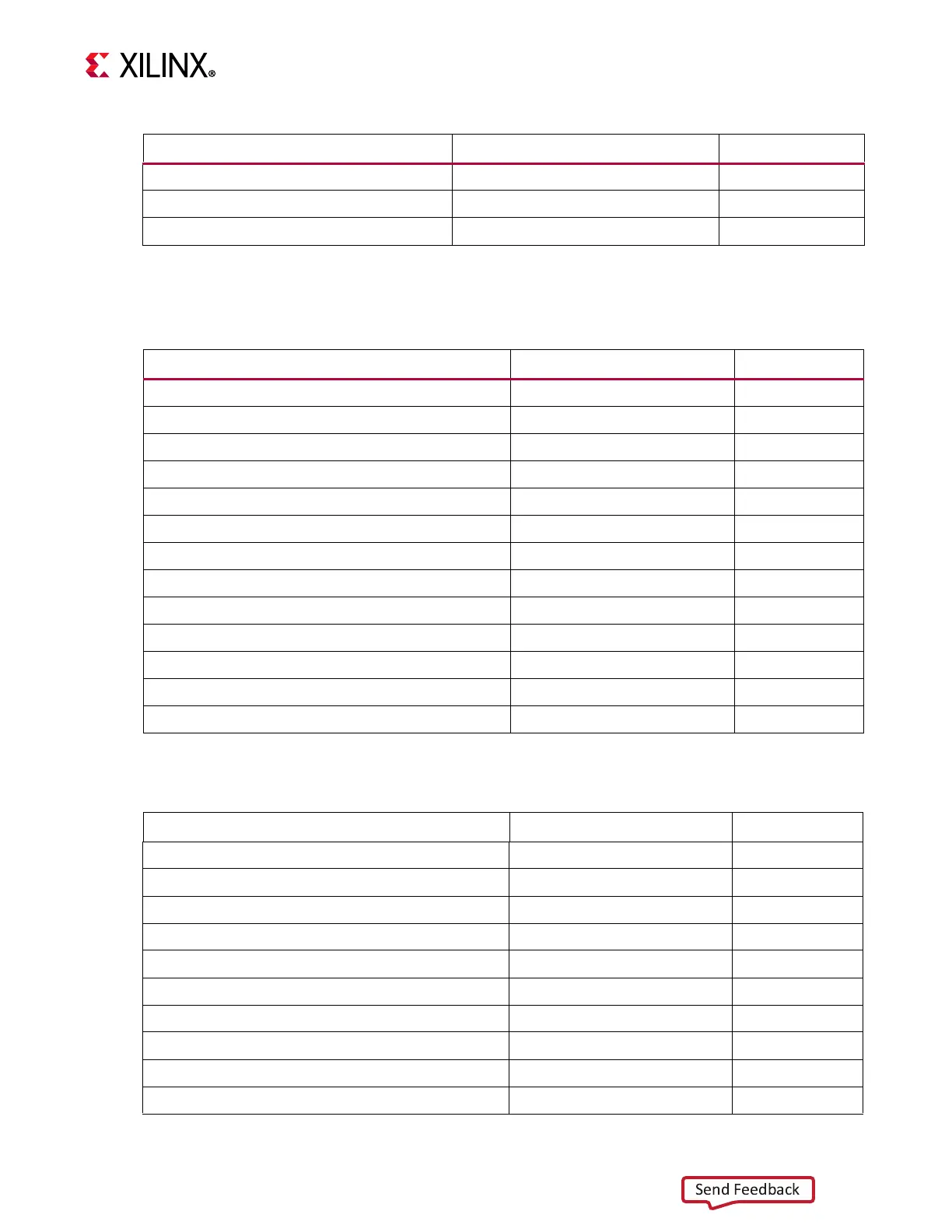

Tab le 5 -4 shows the address map of various IP blocks used in the PL of an SDI design.

Video Processing Subsystem (VPSS-Scaler) 0x00_A020_0000 256K

H.264/H.265 Video Codec Unit (VCU) 0x00_A010_0000 1M

Video PHY Controller 0x00_A006_0000 64K

Table 5-3: Address Map for Ethernet 10G Design IP Blocks

IP Core Base Address Offset

AXI DMA 0x00_B000_0000 4K

HDMI I2C Controller 0x00_A005_0000 4K

HDMI Frame Buffer Read 0x00_A004_0000 64K

HDMI Frame Buffer Write 0 0x00_A001_0000 64K

HDMI Frame Buffer Write 1 0x00_A02B_0000 64K

HDMI Frame Buffer Write 1 0x00_A02C_0000 64K

HDMI 1.4/2.0 Receiver Subsystem v2.0 0x00_A000_0000 64K

HDMI 1.4/2.0 Transmitter Subsystem v2.0 0x00_A002_0000 128K

Video Mixer 0x00_A007_0000 64K

Video Processing Subsystem (VPSS) 0x00_A008_0000 256K

H.264/H.265 Video Codec Unit (VCU) 0x00_A010_0000 1M

Video PHY Controller 0x00_A006_0000 64K

Ethernet 10G/25G Subsystem 0x00_B000_1000 4K

Table 5-4: Address Map for SDI Design IP Blocks

IP Core Base Address Offset

Audio Formatter 0x00_A000_0000 4K

AXI GPIO 0x00_A006_0000 4K

GPIO Resets 0x00_A006_3000 4K

GPIO Registers 0x00_A006_1000 4K

GPIO Registers 0x00_A006_2000 4K

SDI TX Frame buffer read 0x00_B001_0000 64K

Video frame buffer read 0x00_A00C_0000 64K

SDI RX Frame buffer write 0x00_B000_0000 64K

Video frame buffer write 0x00_A00D_0000 64K

Video Mixer 0x00_A007_0000 64K

Table 5-2: Address Map for Audio Design IP Blocks (Cont’d)

IP Core Base Address Offset

Loading...

Loading...