RFSoC Data Converter Evaluation Tool User Guide 49

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 7: Protocol Specification

Socket Interface

The TCP/IP socket protocol is used for the datapath and control path. The LabVIEW GUI

running on the host machine has TCP clients, and the TCP servers are running under the

Linux application on the RFSoC PS. The control path works on TCP port 8081 and datapath

works on TCP port 8082. The TCP socket uses a Linux TCP/IP stack, which uses the GEM

Ethernet controller and driver for sending packets. Because the TCP socket is used, it is

possible to run the GUI on any networked machines.

Control Path

The control interface is a generic command-response interface that can be used to call any

software API or function. Its main purpose is to provide a robust communication method

between a host and client application that allows RFDC hardware control commands to be

issued and responses to be retrieved. All control commands are sent over TCP port 8081. At

a high-level, it is string-based—meaning when supporting a new hardware interface, all that

is required is the ability to send and receive terminated strings over that interface, and the

core code remains unchanged.

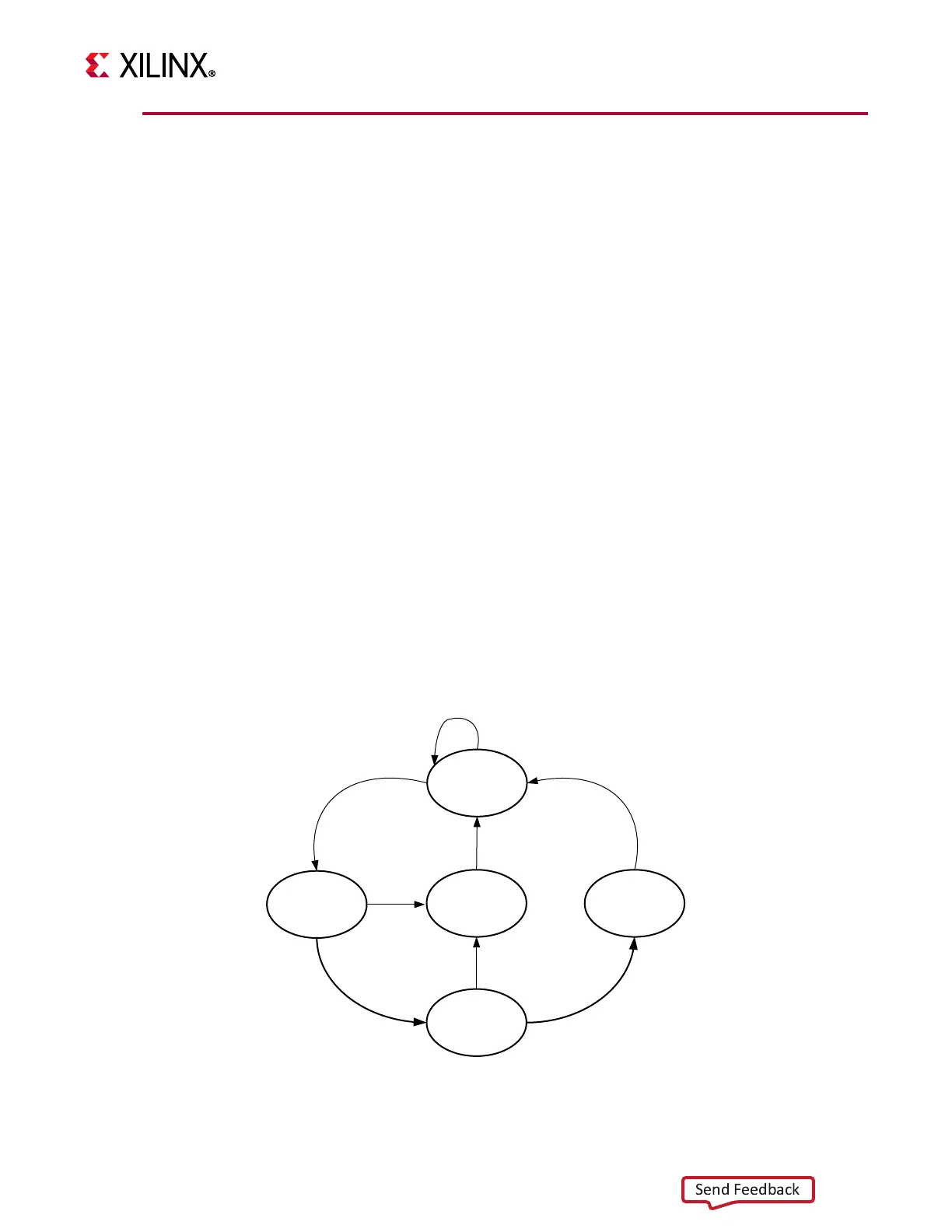

Control Path State Machine

The control path is used to control and configure the RF-ADCs, RF-DACs, or board

peripherals. It uses the I2C client driver or RFDC driver to configure peripherals. Figure 7-2

shows the Control/Command state machine.

X-Ref Target - Figure 7-2

Figure 7-2: Control/Command State Machine

Get

Command

Execute

Parse

Command

Error Return

X21256-090918

Loading...

Loading...