RFSoC Data Converter Evaluation Tool User Guide 61

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 9: System Considerations

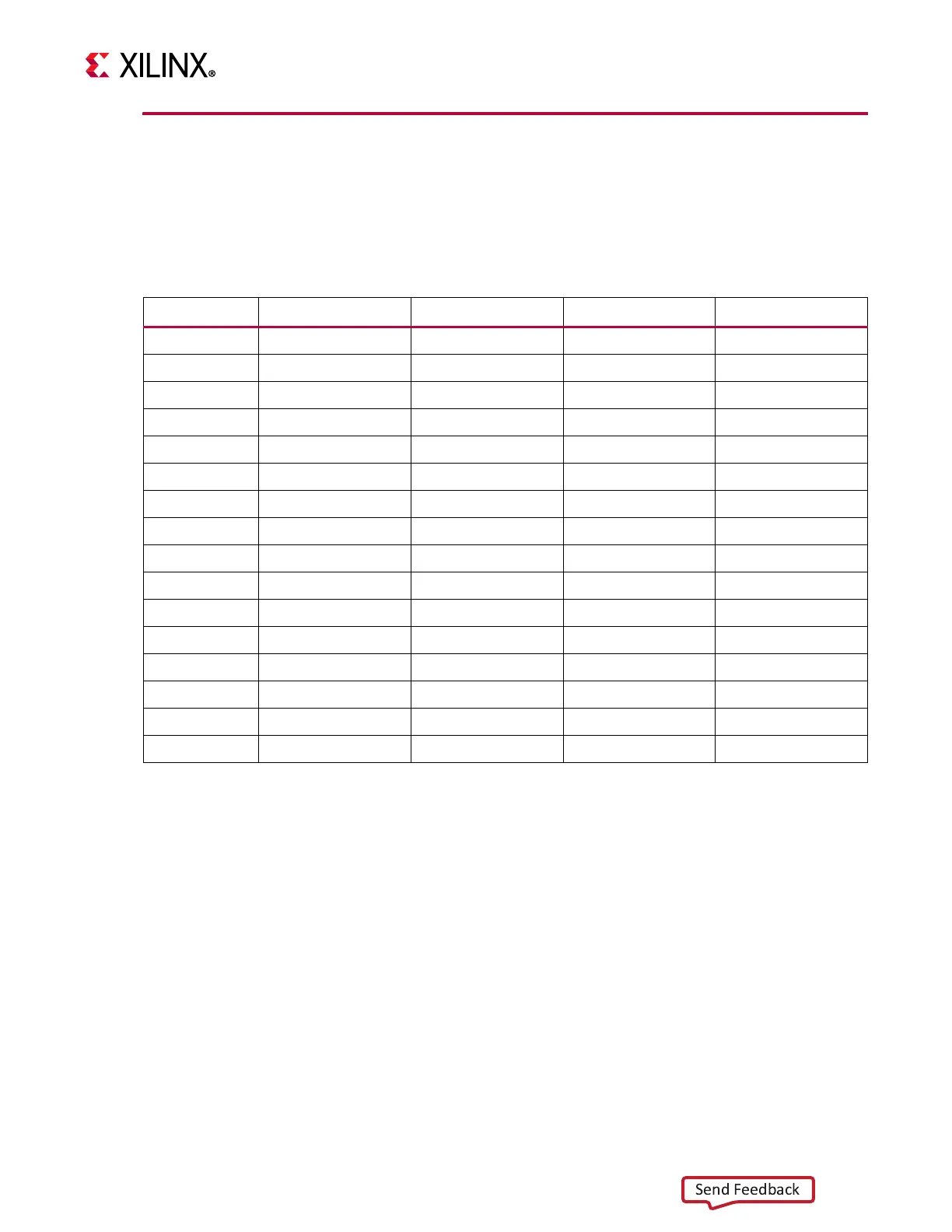

Memory Mapping for RF-DAC/RF-ADC

PL DDR is divided into four partitions (reserved memory), and each partition is 512 MB. It

can run either RF-DAC/RF-ADC from these partitions. It can run either RF-DAC/RF-ADC

from this partition. Table 9-2 lists partitions, their starting address, and their size.

Table 9-2: Memory Mapping for RF-DAC/RF-ADC

Partition DDR Start Address Size Component

1 PL 0x410000000 128MB RF-DAC/RF-ADC

2 PL 0x418000000 128MB RF-DAC/RF-ADC

3 PL 0x420000000 128MB RF-DAC/RF-ADC

4 PL 0x428000000 128MB RF-DAC/RF-ADC

5 PL 0x430000000 128MB RF-DAC/RF-ADC

6 PL 0x438000000 128MB RF-DAC/RF-ADC

7 PL 0x440000000 128MB RF-DAC/RF-ADC

8 PL 0x448000000 128MB RF-DAC/RF-ADC

9 PL 0x450000000 128MB RF-DAC/RF-ADC

10 PL 0x458000000 128MB RF-DAC/RF-ADC

11 PL 0x460000000 128MB RF-DAC/RF-ADC

12 PL 0x468000000 128MB RF-DAC/RF-ADC

13 PL 0x470000000 128MB RF-DAC/RF-ADC

14 PL 0x478000000 128MB RF-DAC/RF-ADC

15 PL 0x480000000 128MB RF-DAC/RF-ADC

16 PL 0x488000000 128MB RF-DAC/RF-ADC

Loading...

Loading...