RFSoC Data Converter Evaluation Tool User Guide 41

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 5: Evaluation Tool System Configuration using the GUI

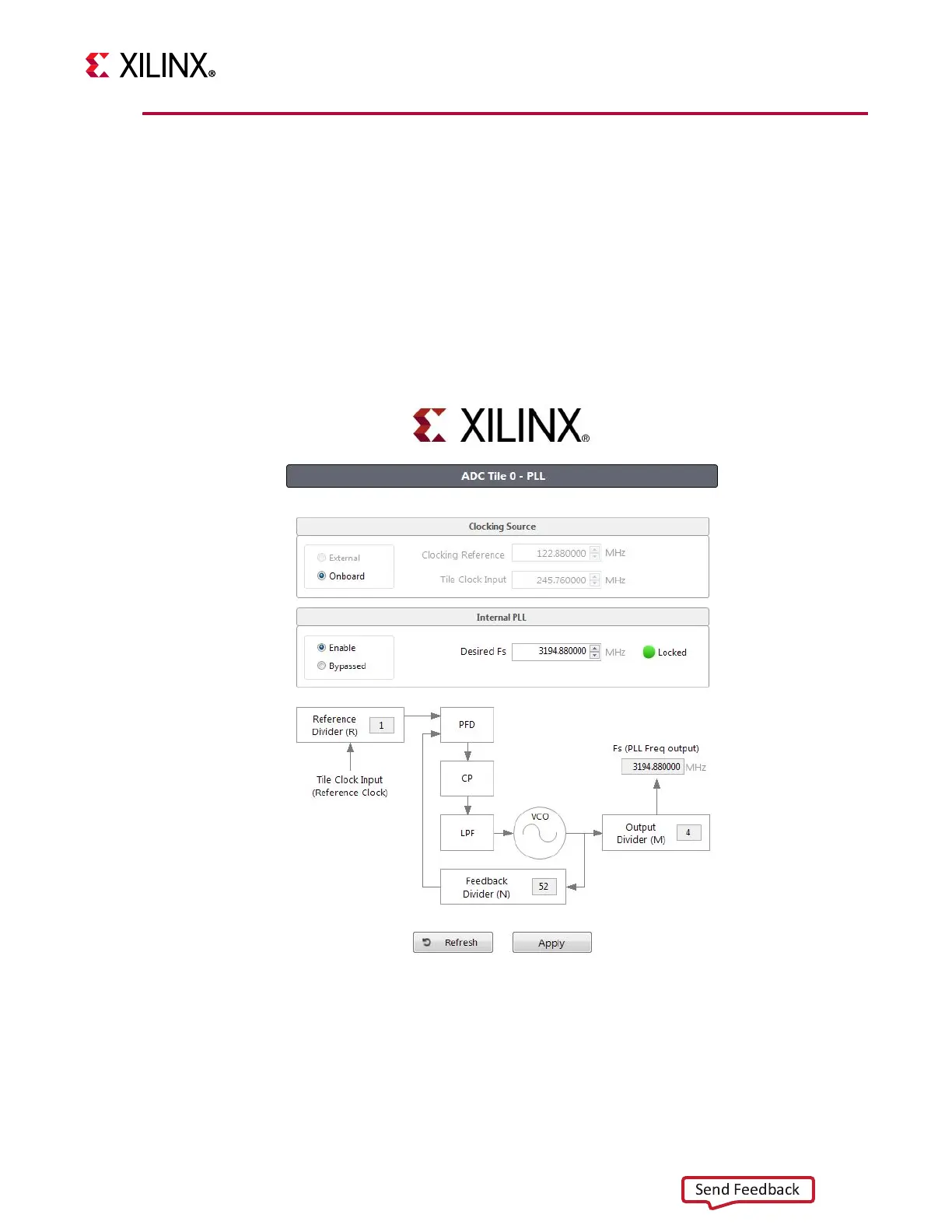

ADC Clock Configuration

The GUI supports:

• Selection of external or internal (PLL) sample clock options

• On-chip PLL configuration for internal sample clock generation (see Figure 5-5).

• The configuration of the RF PLLs on the evaluation board for external clocking

Note:

RFPLL (LMK) is also used to set up the reference clock for the on-chip PLLs. The nominal

settings are 245.76 MHz or 491.52 MHz, for example.

X-Ref Target - Figure 5-5

Figure 5-5: ADC Internal PLL

Loading...

Loading...