RFSoC Data Converter Evaluation Tool User Guide 37

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

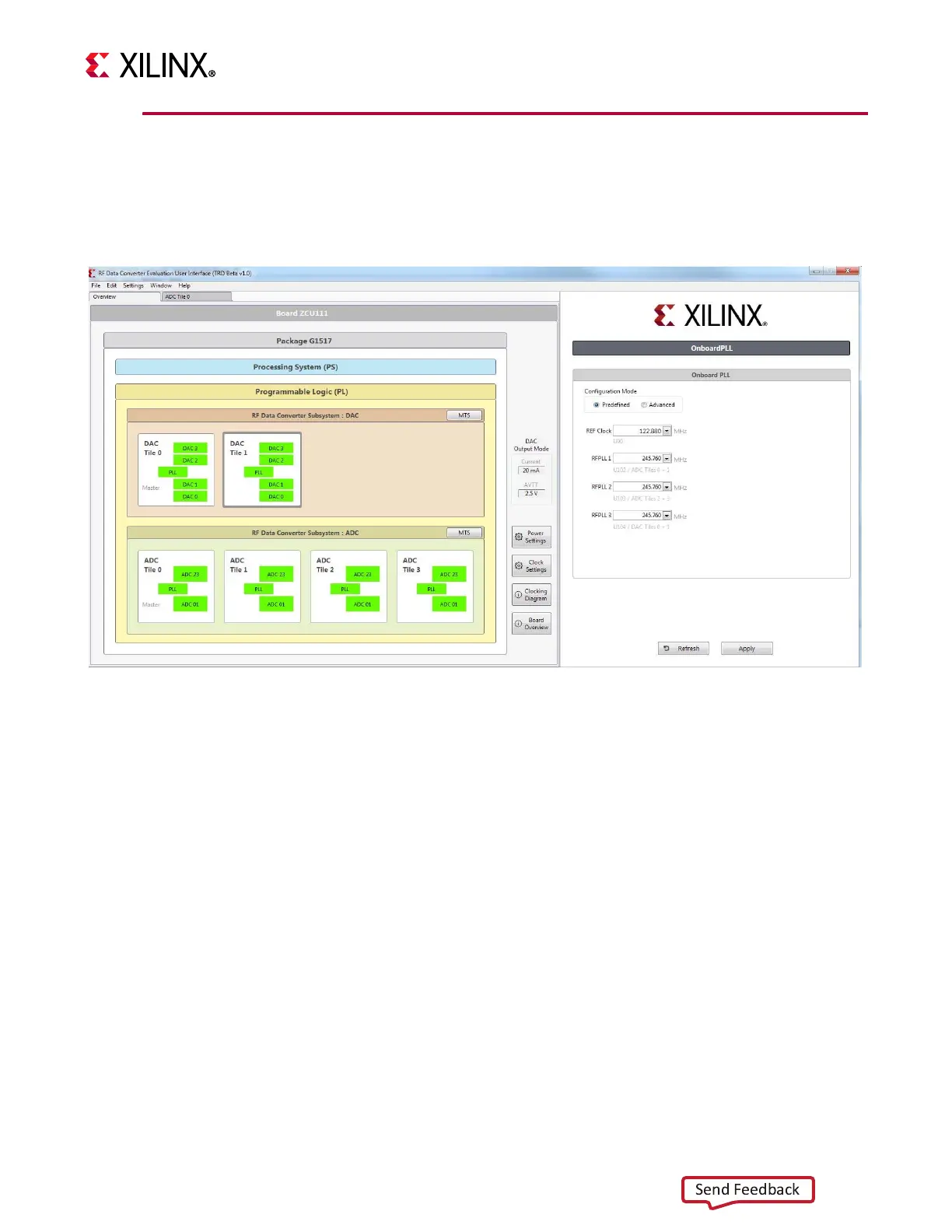

Chapter 5: Evaluation Tool System Configuration using the GUI

External Component Configuration

In the overview tab, when clicking on Clock Settings, the external PLL can be configured

with a set of predefined frequencies as shown in Figure 5-1.

When clicking on Power Settings, the DAC power mode can be changed between 20 mA

and 32 mA.

X-Ref Target - Figure 5-1

Figure 5-1: Overview of External PLLs

Loading...

Loading...