RFSoC Data Converter Evaluation Tool User Guide 24

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 3: Hardware Design

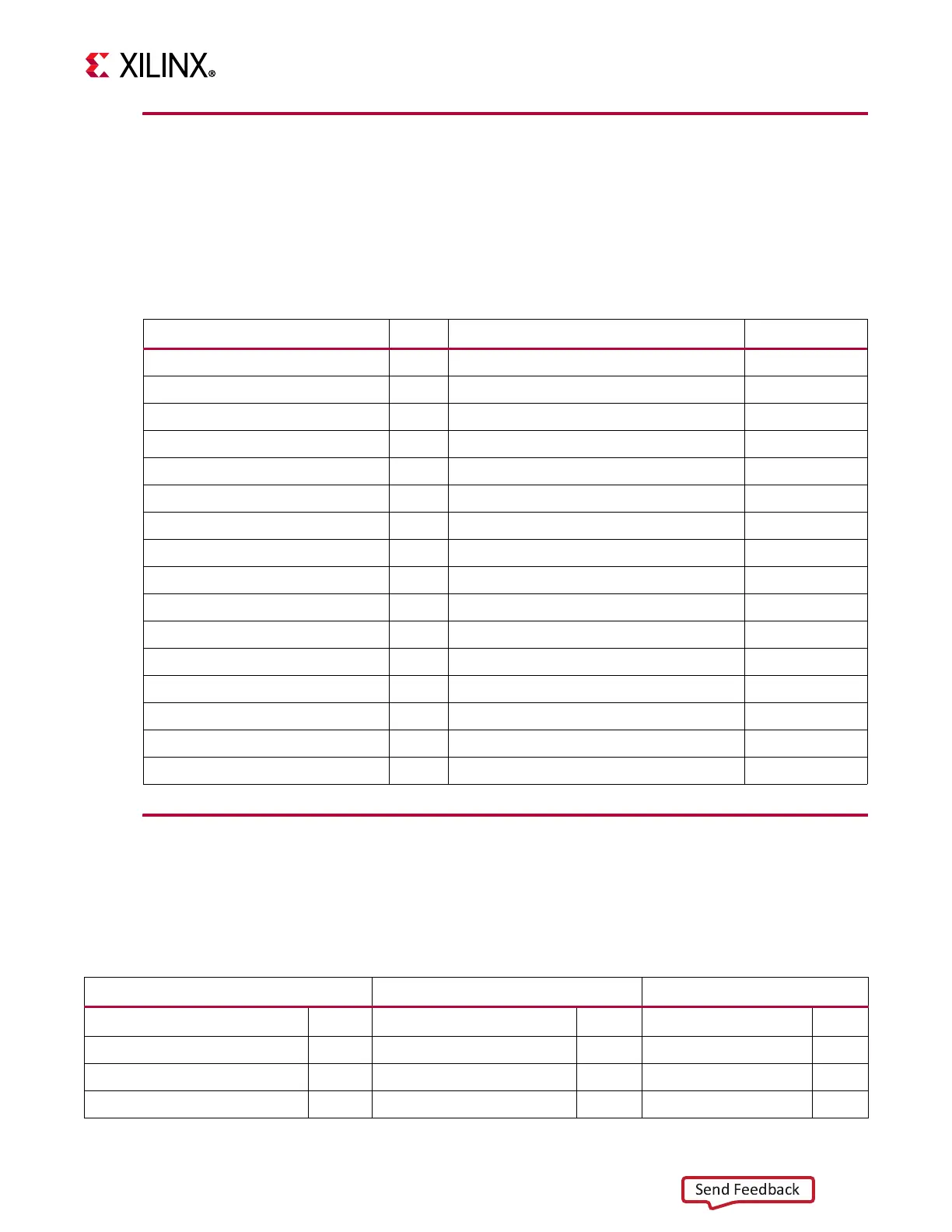

Stream Pipes Control and Status Registers

The register sets in the design are available under the user_axilite_control block. The block

has an AXI4-Lite interface through which the registers can be accessed. In the current

implementation, the base address of the user_axilite_control is 0xB005_0000. Table 3-1 lists

the registers that are available currently.

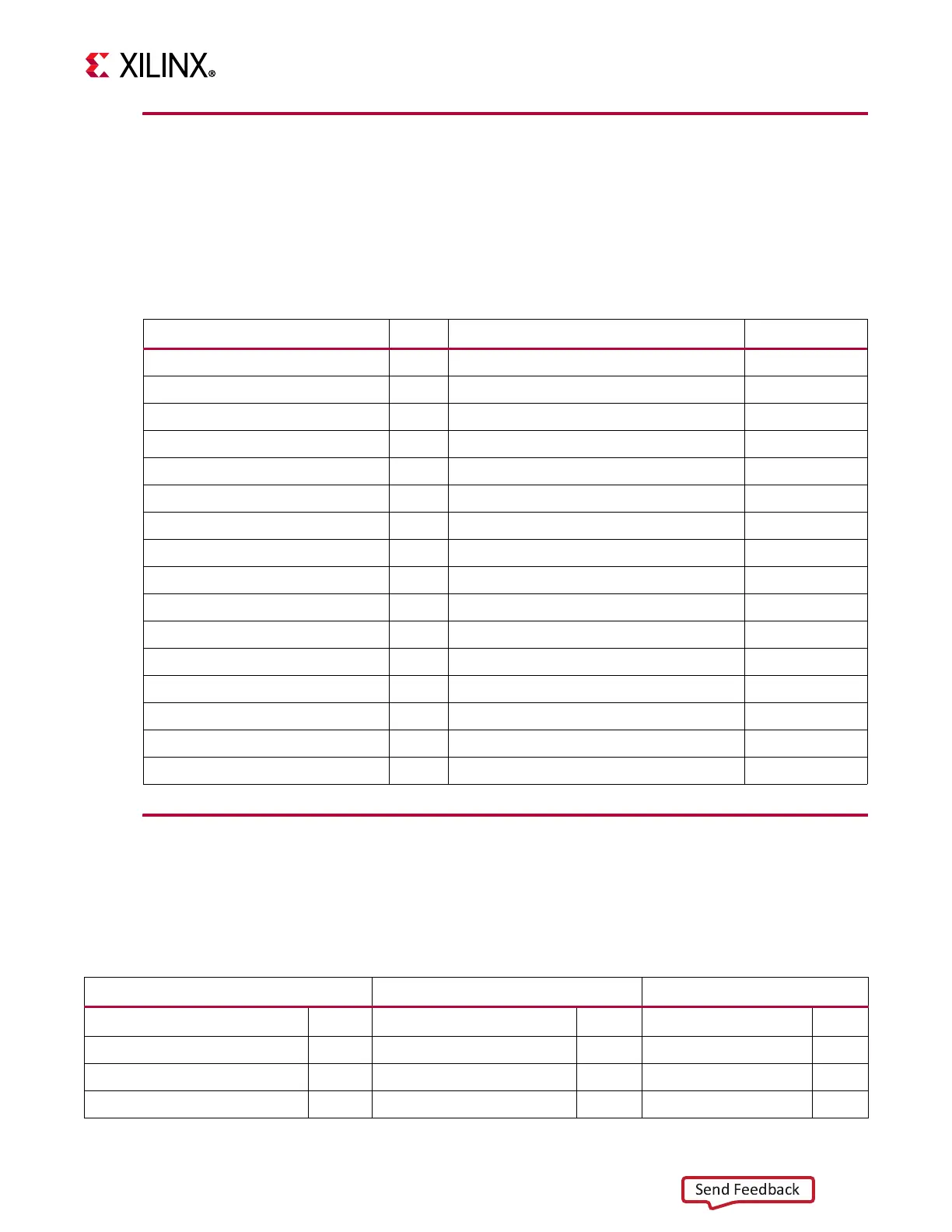

GPIO Selection

Table 3-2 provides the list of GPIOs for channel control, memory loopback reset, and IQ

selection.

Table 3-1: Control and Status Register

Name Offset Description Default Value

DAC_path_0_fifo_data_count 0x00 Indicates the count inside the FIFO 32'd0

DAC_path_1_fifo_data_count 0x04 Indicates the count inside the FIFO 32'd0

DAC_path_2_fifo_data_count 0x08 Indicates the count inside the FIFO 32'd0

DAC_path_3_fifo_data_count 0x0C Indicates the count inside the FIFO 32'd0

DAC_path_4_fifo_data_count 0x10 Indicates the count inside the FIFO 32'd0

DAC_path_5_fifo_data_count 0x14 Indicates the count inside the FIFO 32'd0

DAC_path_6_fifo_data_count 0x18 Indicates the count inside the FIFO 32'd0

DAC_path_7_fifo_data_count 0x1C Indicates the count inside the FIFO 32'd0

ADC_path_0_fifo_data_count 0x20 Indicates the count inside the FIFO 32'd0

ADC_path_1_fifo_data_count 0x24 Indicates the count inside the FIFO 32'd0

ADC_path_2_fifo_data_count 0x28 Indicates the count inside the FIFO 32'd0

ADC_path_3_fifo_data_count 0x2C Indicates the count inside the FIFO 32'd0

ADC_path_4_fifo_data_count 0x30 Indicates the count inside the FIFO 32'd0

ADC_path_5_fifo_data_count 0x34 Indicates the count inside the FIFO 32'd0

ADC_path_6_fifo_data_count 0x38 Indicates the count inside the FIFO 32'd0

ADC_path_7_fifo_data_count 0x3C Indicates the count inside the FIFO 32'd0

Table 3-2: Control Signals

DAC ADC Common

Function GPIO# Function GPIO# Function GPIO#

DAC0 Memory Loopback Reset 0 ADC0001 FIFO Reset 32 DAC Arbiter Reset 64

Reserved 1 ADC0001_IQ_Merge_sel 33 ADC Arbiter Reset 65

DAC0 Channel Control 2 ADC0001 Channel Control 34 Reserved 66

Loading...

Loading...