RFSoC Data Converter Evaluation Tool User Guide 23

UG1287 (v2018.2) October 1, 2018 www.xilinx.com

Chapter 3: Hardware Design

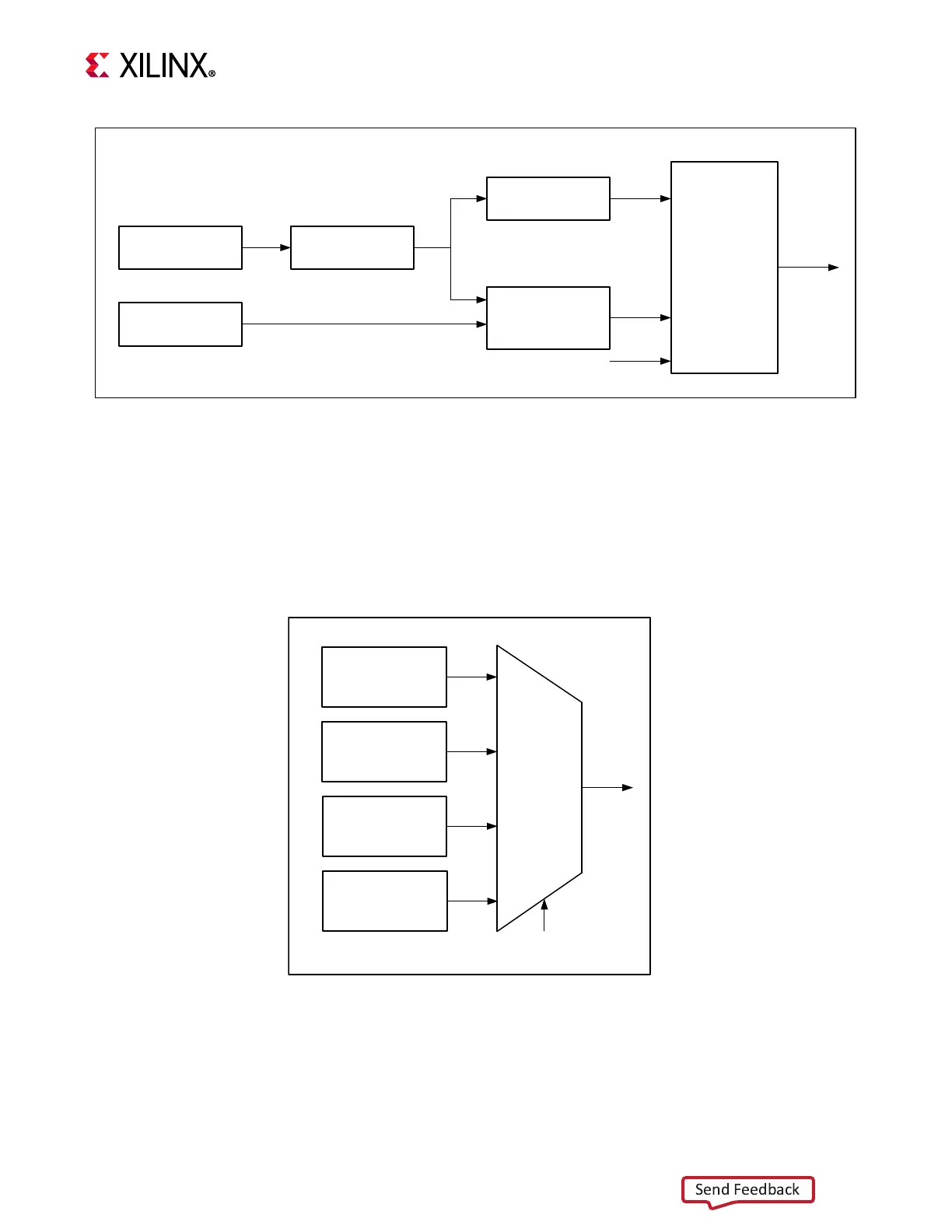

Channel Select MUX

The Channel MUX implementation is an 8:1 streaming selection logic as shown in

Figure 3-11. Among eight incoming streaming inputs, only one streaming data is passed to

SG DMA interface based on channel-select input.

X-Ref Target - Figure 3-10

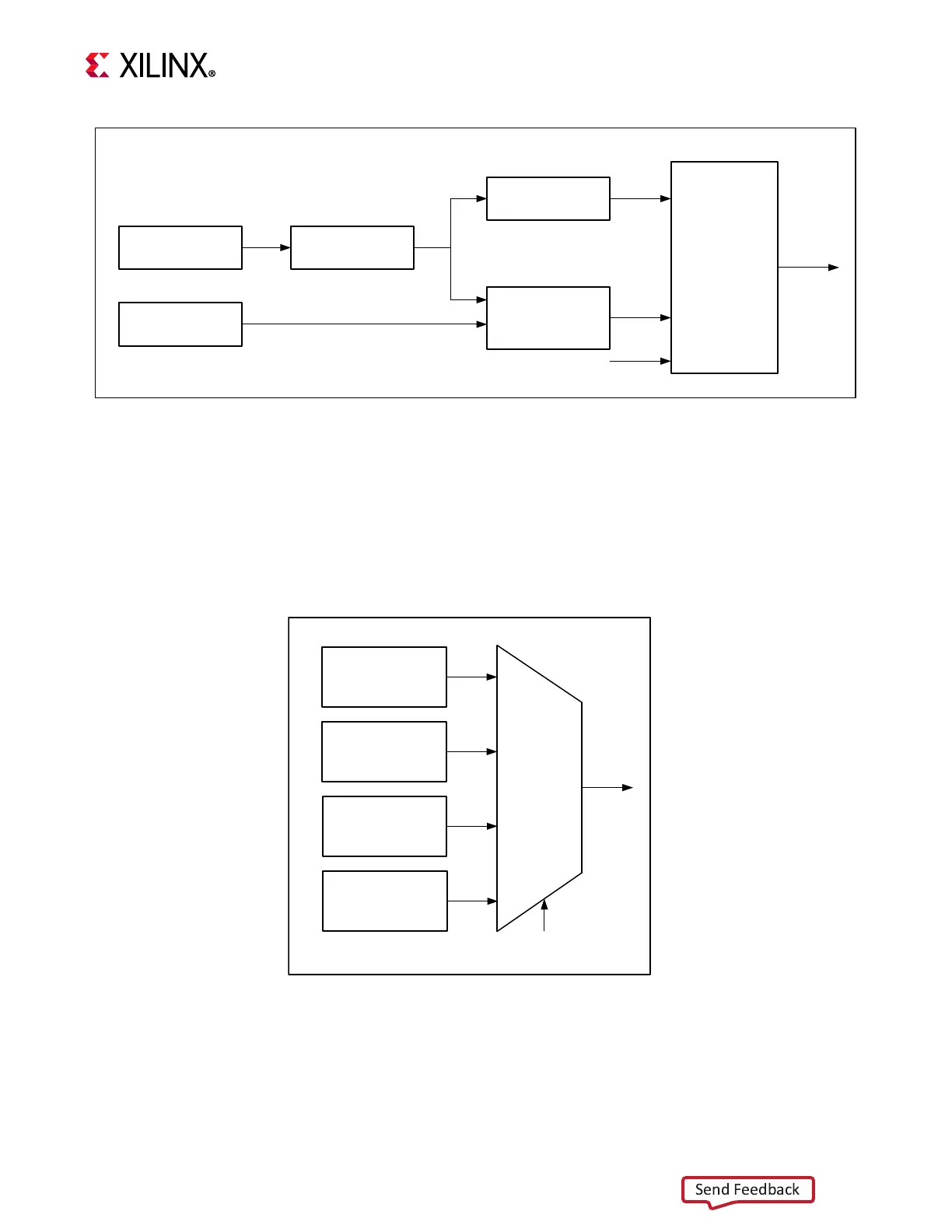

Figure 3-10: IQ Datapath

I (Real) Stream

Q Stream

AXIS Broadcaster

Data Width

Converter

AXIS Combiner

AXI4-Stream

Mux

DMA

IQ Select

X21242-091318

X-Ref Target - Figure 3-11

Figure 3-11: Channel MUX

AXIS FIFO

0

AXIS FIFO

1

------------

AXIS FIFO

7

Channel Select

Channel

Select Mux

Stream

Out to

DMA

X21243-090918

Loading...

Loading...