ZYNQ Ultrascale + FPGA Board AXU2CGA/B User Manual

Amazon Store: https://www.amazon.com/alinx

USB3.0 Reference Clock

Positive

USB3.0 Reference Clock

Negative

USB2.0 Data Direction Signal

USB2.0 the NEXT Data Signal

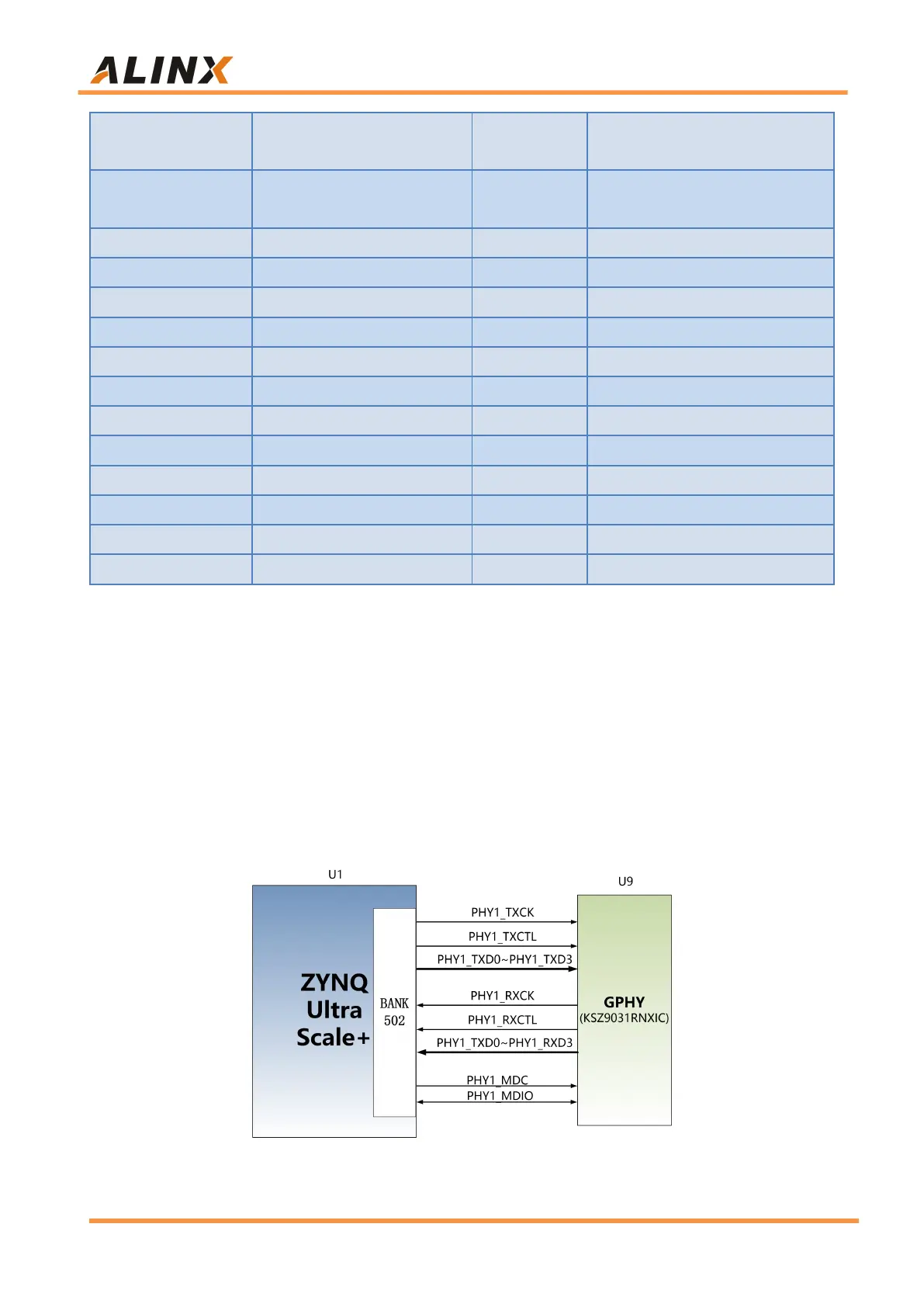

Part 9: Gigabit Ethernet Interface

There is 1 Gigabit Ethernet interface on AXU2CGA/B, and the Ethernet

interface is on BANK502 of PS connected through GPHY chip. The GPHY chip

uses the KSZ9031RNXIC Ethernet PHY chip from Micrel, and the PHY

Address is 001. Figure 9-1 is a schematic diagram of the connection of the

Ethernet PHY chip on the ZYNQ PS side:

Figure 9-1: ZYNQ PS System and GPHY Schematic

Loading...

Loading...