AT90S4414/8515

23

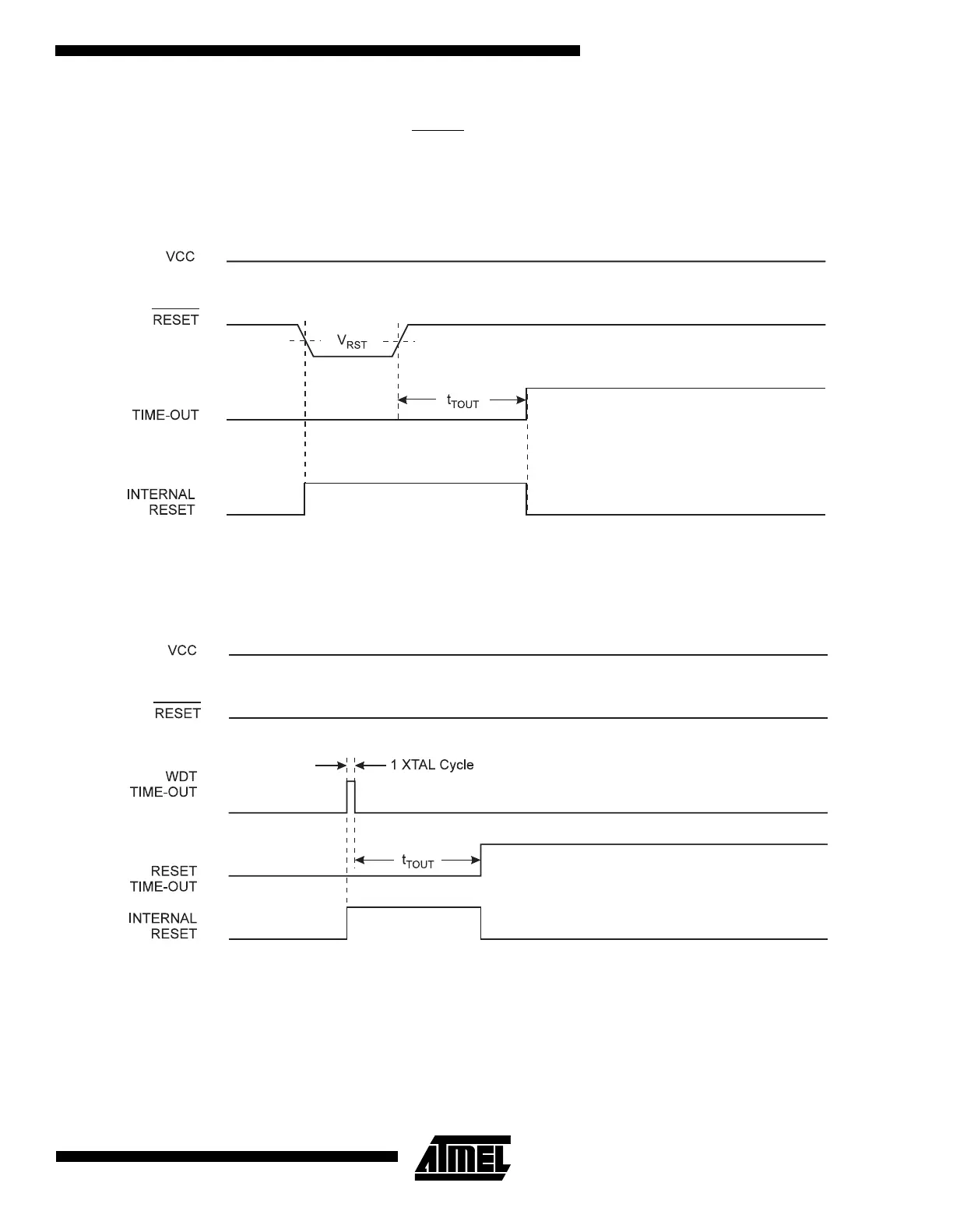

External Reset

An external reset is generated by a low level on the RESET

pin. Reset pulses longer than 50 ns will generate a reset, even

if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the

Reset Threshold Voltage - V

RST

on its positive edge, the delay timer starts the MCU after the Time-out period t

TOUT

has

expired.

Figure 26. External Reset During Operation

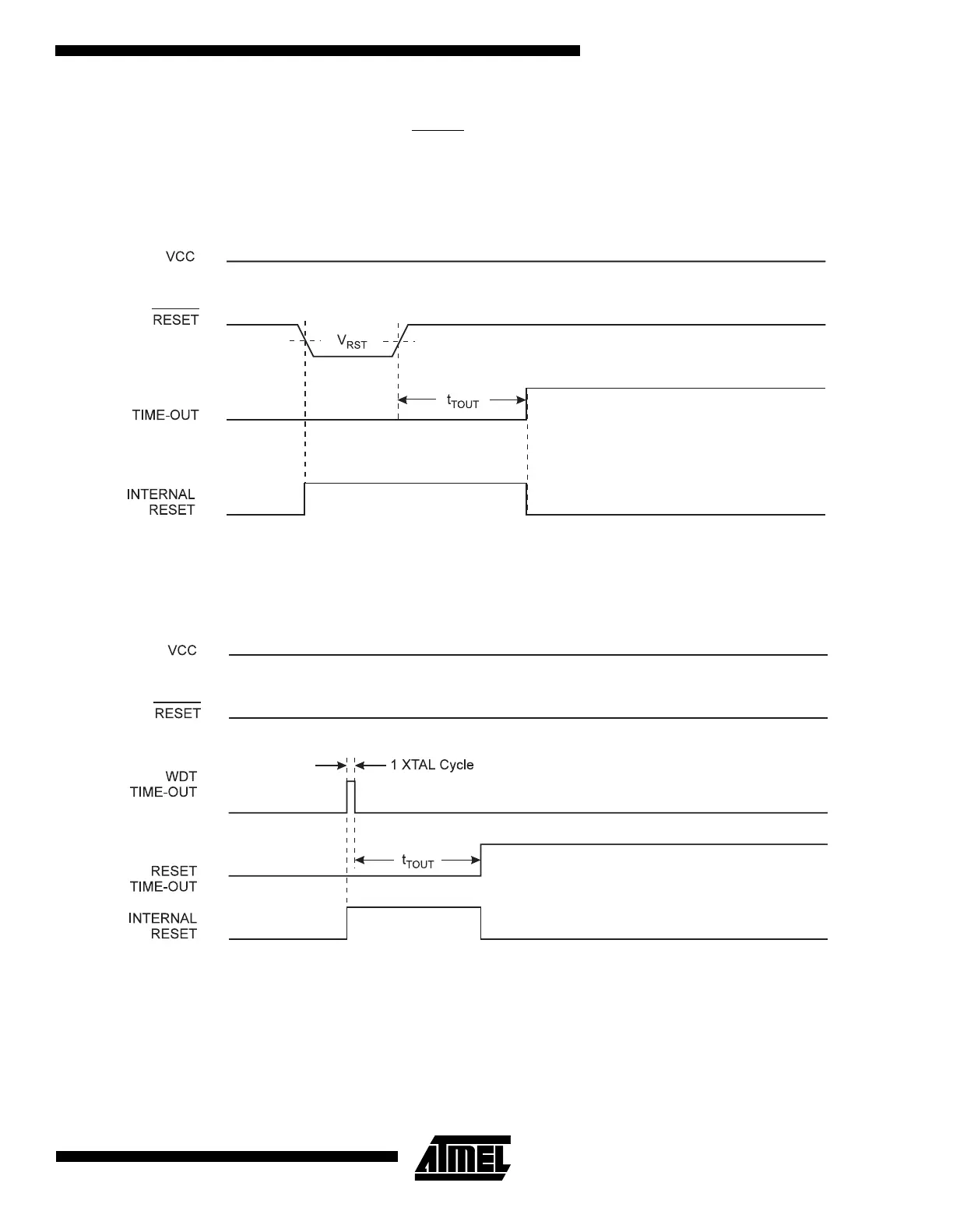

Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of 1 XTAL cycle duration. On the falling edge of this

pulse, the delay timer starts counting the Time-out period t

TOUT

. Refer to page 38 for details on operation of the Watchdog.

Figure 27. Watchdog Reset During Operation

Loading...

Loading...