AT90S4414/8515

84

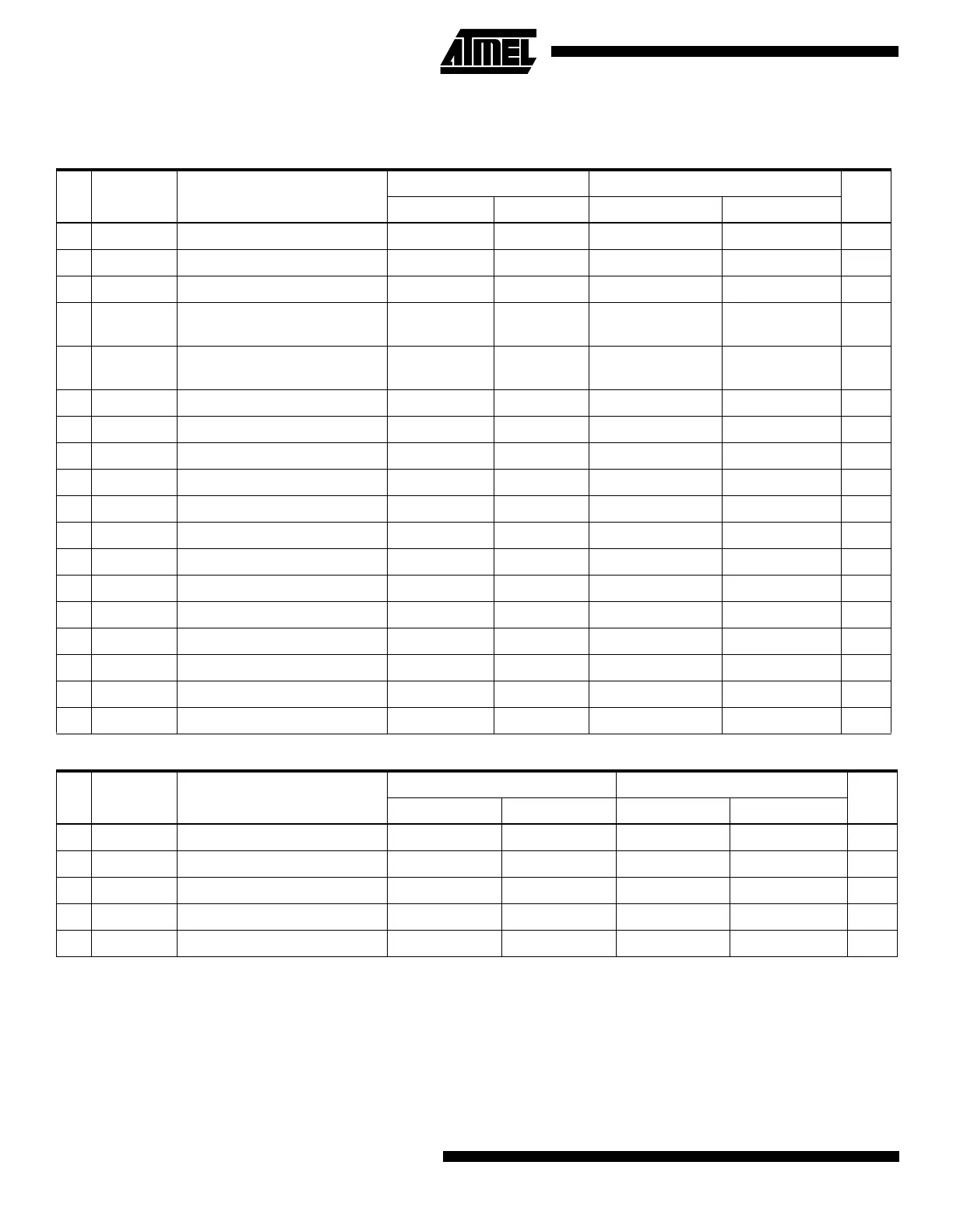

External Data Memory Timing

Notes: 1. This assumes 50% clock duty cycle. The half period is actually the high time of the external clock, XTAL1.

2. This assumes 50% clock duty cycle. The half period is actually the low time of the external clock, XTAL1.

Table 38. External Data Memory Characteristics, 4.0 - 6.0 Volts, No Wait State

Symbol Parameter

8 MHz Oscillator Variable Oscillator

UnitMin Max Min Max

01/t

CLCL

Oscillator Frequency 0.0 8.0 MHz

1t

LHLL

ALE Pulse Width 32.5 0.5t

CLCL

-30.0

(1)

ns

2t

AVLL

Address Valid A to ALE Low 22.5 0.5t

CLCL

-40.0

(1)

ns

3a t

LLAX_ST

Address Hold After ALE Low,

ST/STD/STS Instructions

67.5 0.5t

CLCL

+5.0

(2)

ns

3b t

LLAX_LD

Address Hold after ALE Low,

LD/LDD/LDS Instructions

15.0 15.0

ns

4t

AVLLC

Address Valid C to ALE Low 22.5 0.5t

CLCL

-40.0

(1)

ns

5t

AVRL

Address Valid to RD Low 95.0 1.0t

CLCL

-30.0 ns

6t

AVWL

Address Valid to WR Low 157.5 1.5t

CLCL

-30.0

(1)

ns

7t

LLWL

ALE Low to WR Low 105.0 145 1.0t

CLCL

-20.0 1.0t

CLCL

+20.0 ns

8t

LLRL

ALE Low to RD Low 42.5 82.5 0.5t

CLCL

-20.0

(2)

0.5t

CLCL

+20.0

(2)

ns

9t

DVRH

Data Setup to RD High 60.0 60.0 ns

10 t

RLDV

Read Low to Data Valid 70.0 1.0t

CLCL

-55.0 ns

11 t

RHDX

Data Hold After RD High 0.0 0.0 ns

12 t

RLRH

RD Pulse Width 105.0 1.0t

CLCL

-20.0 ns

13 t

DVWL

Data Setup to WR Low 27.5 0.5t

CLCL

-35.0

(2)

ns

14 t

WHDX

Data Hold After WR High 0.0 0.0 ns

15 t

DVWH

Data Valid to WR High 95.0 1.0t

CLCL

-30.0 ns

16 t

WLWH

WR Pulse Width 42.5 0.5t

CLCL

-20.0

(1)

ns

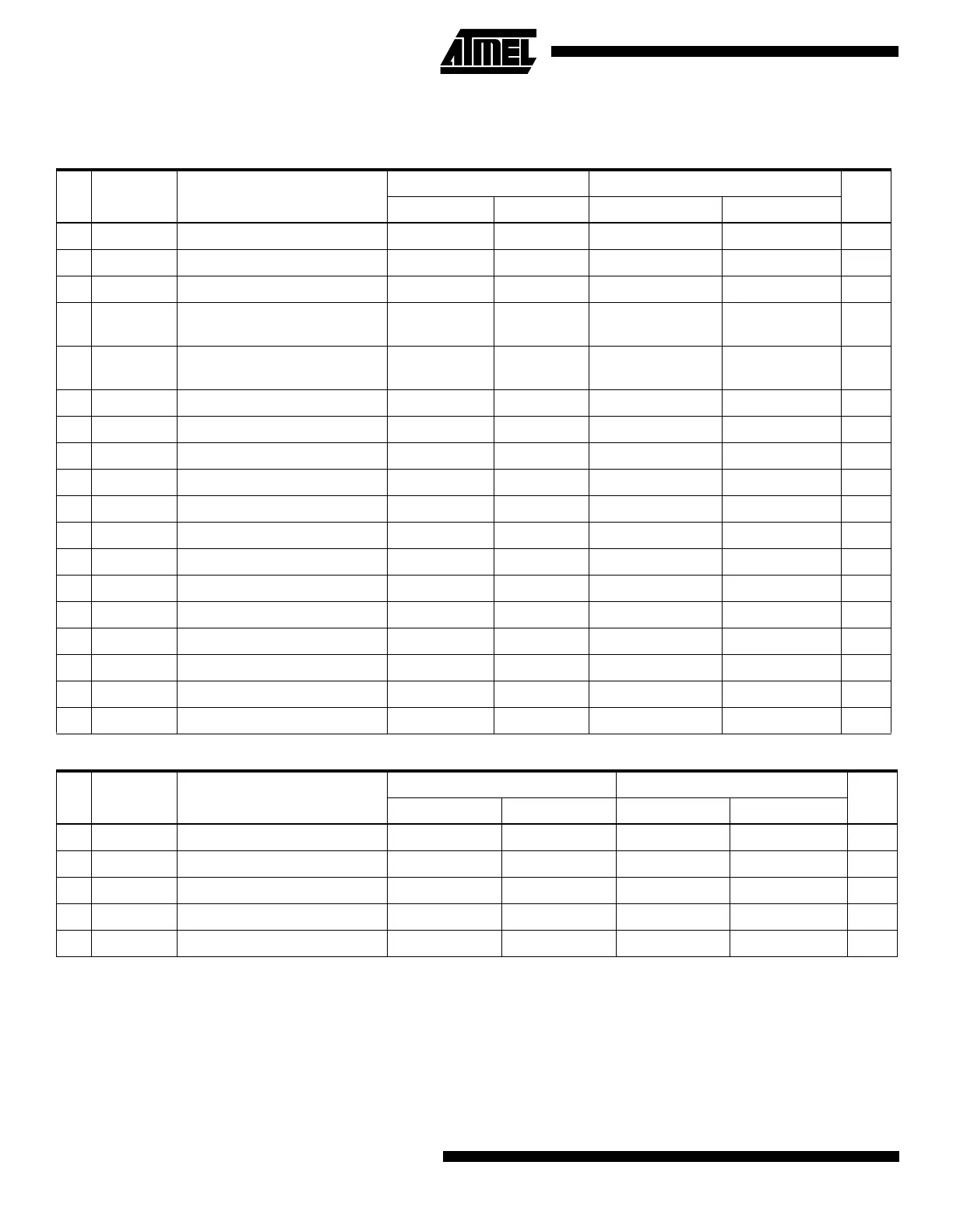

Table 39. External Data Memory Characteristics, 4.0 - 6.0 Volts, 1 Cycle Wait State

Symbol Parameter

8 MHz Oscillator Variable Oscillator

UnitMin Max Min Max

01/t

CLCL

Oscillator Frequency 0.0 8.0 MHz

10 t

RLDV

Read Low to Data Valid 195.0 2.0t

CLCL

-55.0 ns

12 t

RLRH

RD Pulse Width 230.0 2.0t

CLCL

-20.0 ns

15 t

DVWH

Data Valid to WR High 220.0 2.0t

CLCL

-30.0 ns

16 t

WLWH

WR Pulse Width 167.5 1.5t

CLCL

-20.0

(2)

ns

Loading...

Loading...