IPC@CHIP - SC12

Hardware Manual v1.1 [05.11.2002]

©BECK IPC GmbH page 22 of 28

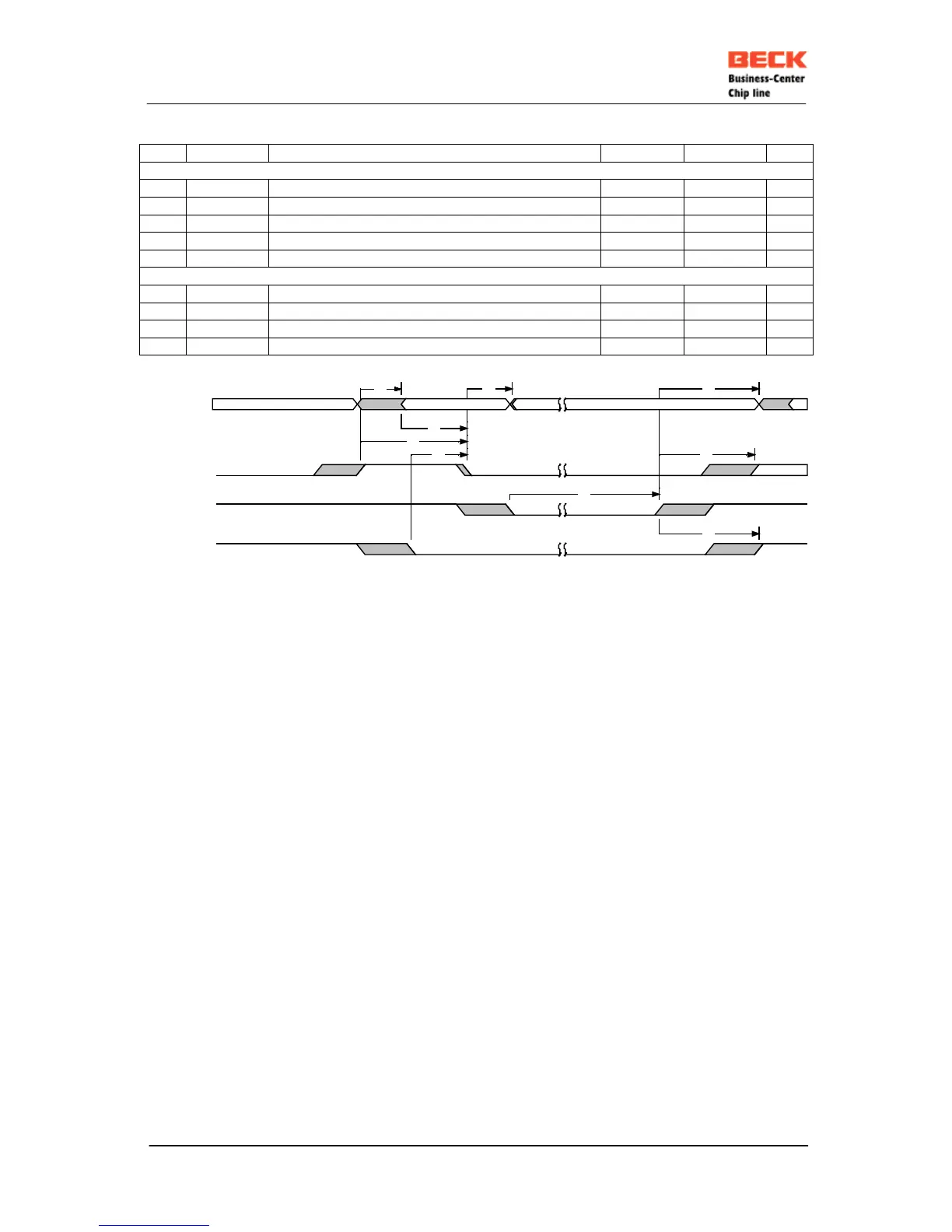

8.4.2 Write Cycle

No. Symbol Description Min Max Unit

General Timing Responses

10 t

LHLL

ALE Width 40 ns

12 t

AVLL

AD Address Valid to ALE Low 23 ns

17 T

CXCSX

PCSx# Hold from Read Inactive 23 ns

23 T

LHAV

ALE High to Address Valid 20 ns

99 T

PLAL

PCSx# Active to ALE Inactive 15 28 ns

Read Cycle Timing Responses

32 T

WLWH

Write Pulse Width - PCS0#..PCS3# Active 840 ns

32 T

WLWH

Write Pulse Width – PCS5#, PCS6# Active 240 ns

33 T

WHLH

Write Inactive to ALE High 23 ns

34 T

WHDX

Data Hold after Write Inactive 40 ns

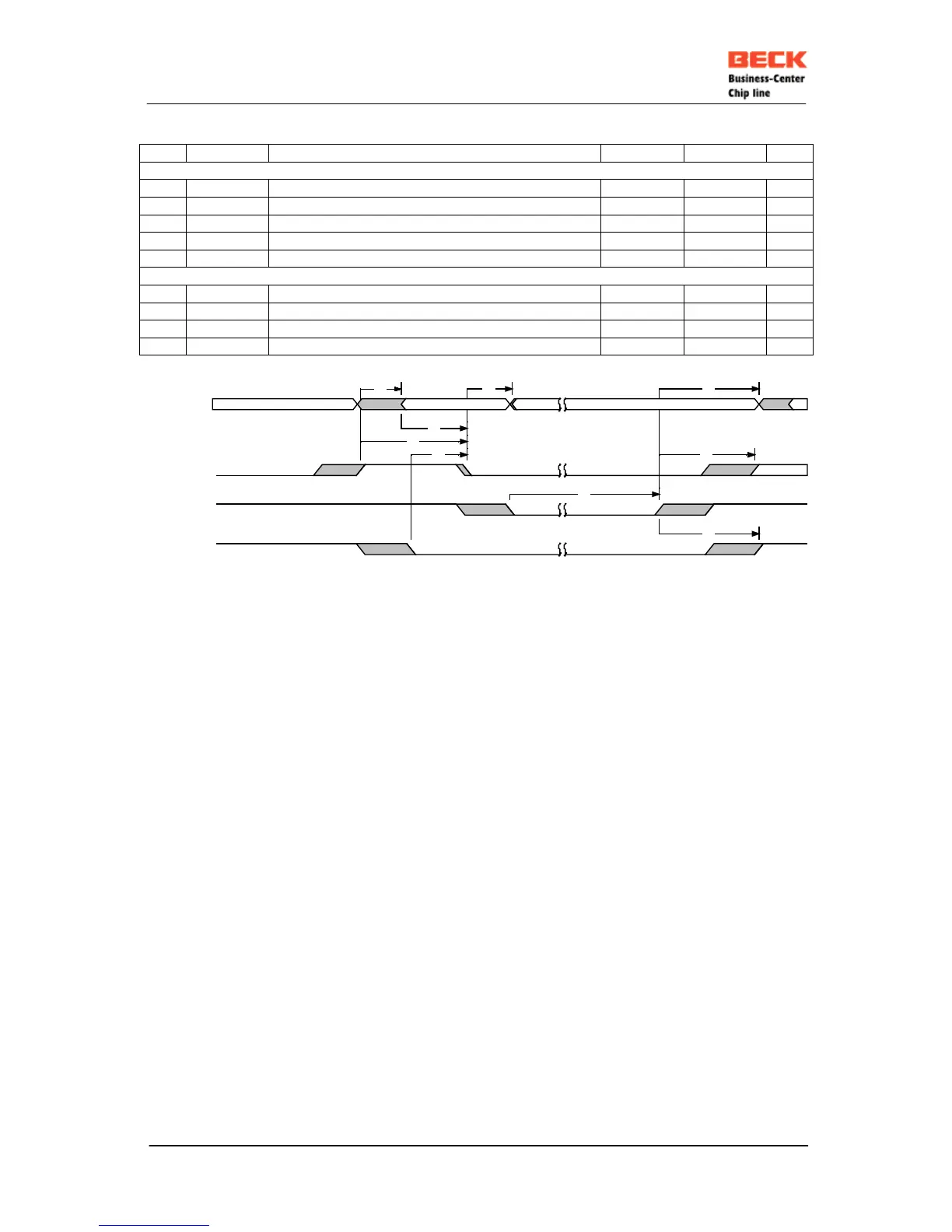

Addres

Data

17

32

33

12

99

10

341323

AD0..AD7

ALE

WR#

PCSx#

*) the falling edge of PCS1# is 50nS delayed internaly

8.4.3 Interrupt Acknowledge Cycle

Currently not supported by software

Loading...

Loading...