GE MEDICAL SYSTEMS CT 9800 QUICK SYSTEM

Rev. 14 Direction 18000

4-3-29

The entire self-test takes approx. 1 second to execute. During execution, various LED’s will light and after the 1

second execution, all LED’s should be off. If a failure is detected, the RED LED’s will remain ON or will flash a

specific number of times to indicate what the failure is (see note below).

Note: To decode the flashing LED pattern and determine the cause of failure, follow these guidelines: The

LED’s flash two times per second. After they have flashed their code, there is a 2 second pause and the code is

repeated. Therefore, wait for the two second pause; then count the number of flashes until the next two second

pause. The number of flashes is used to look up the failing subtest (CODE) in

Tables 4-3-1 and 4-3-2.

PRECAUTION:

If self tests fail during the initial installation, be sure to reseat the controller board. Be sure it is fully seated into

the backplane connector and all Cables are securely attached.

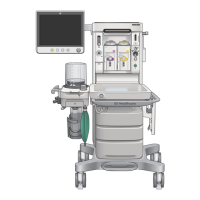

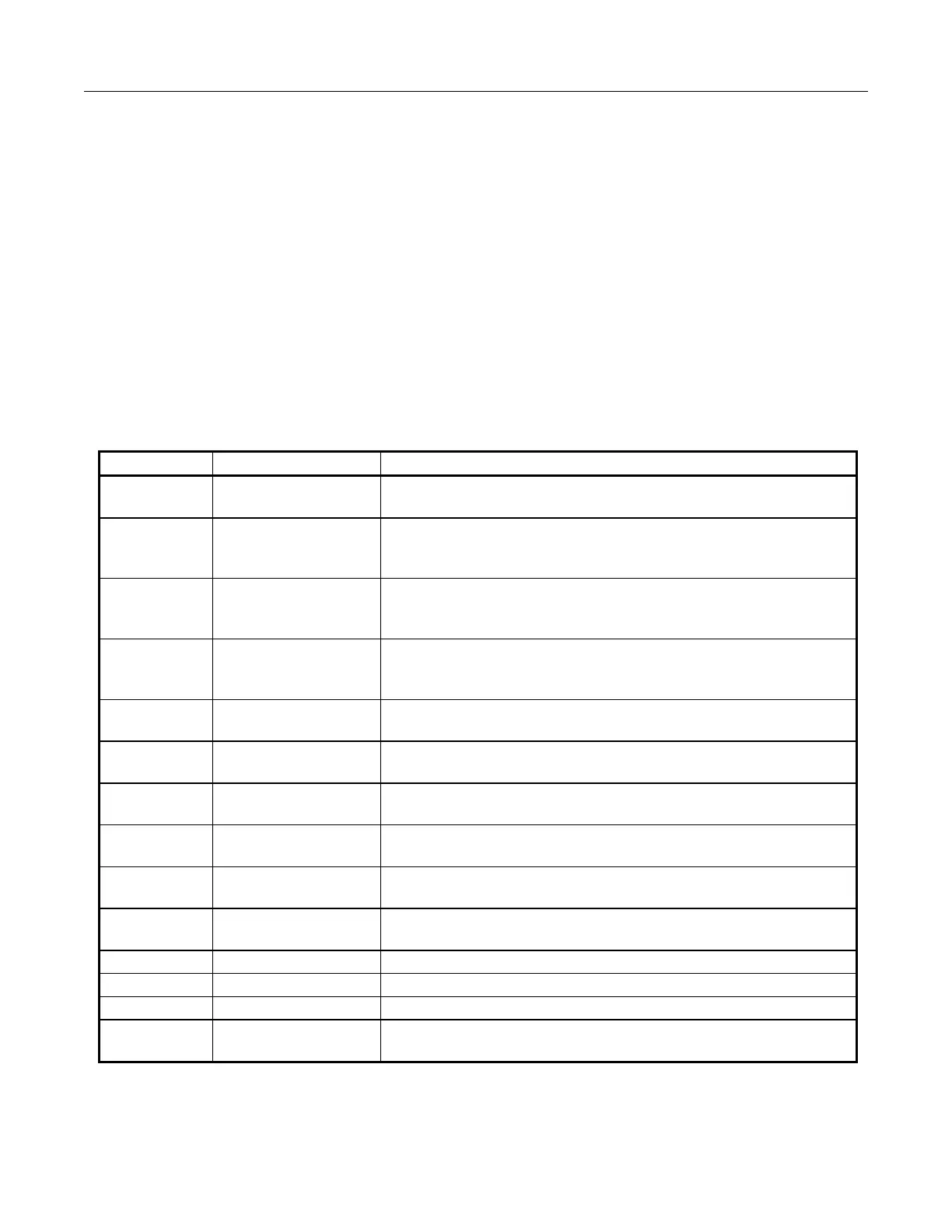

TABLE 4-3-1

HOST MODULE ERROR CODES

Data read from ram did not compare with data written. RAM chips,

ADR Bus, SD Bus, RAM EN, Read or Write problem.

Data read buffer 1 did not compare with data written. Buffer ram

chips, HS BUF EN, HS Address counters, ADR Bus, SD Bus, or

Data read from buffer 2 did not compare with data written. Buffer

ram chips, HS BUF EN, HS Address counter, ADR Bus, SD Bus, or

The done flip-flop did not set or did not clear when told to. Flip-flop,

ADR Bus, SD Bus, I/O decode, or board received a start or reset

Burst counters did not count correctly. Burst counters, ADR Bus,

AD Bus, BMC logic, or burst count latch.

Break counters did not count correctly. Break counters, ADR Bus,

SD Bus. BMC logic, or burst count latch.

Data read back from BMC did not compare with data written. BMC

Data read back from the BMC did not compare with data written.

The checksum at the end of the EEPROM did not compare with the

Data read from dual port ram B did not compare with data written to

dual port ram A. Dual port ram chjps or 80186 not running.

Data Parity or ECC error was not successfully cleared. Test

condition logic, data parity logic, 9520 or FW Bus.

Loading...

Loading...